20 Punkte - Ing. H. Heuermann

20 Punkte - Ing. H. Heuermann

20 Punkte - Ing. H. Heuermann

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

__________________________________<br />

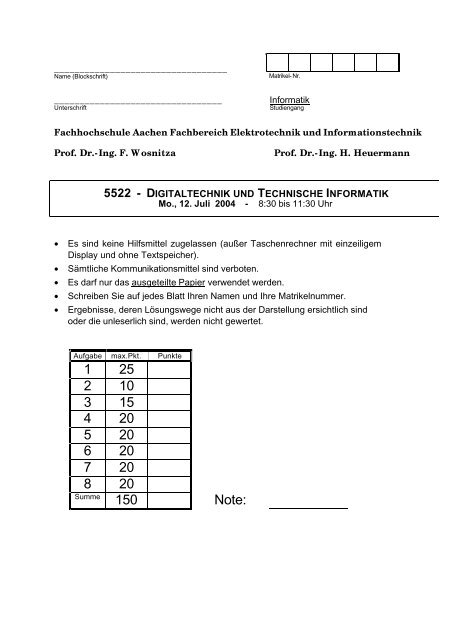

Name (Blockschrift)<br />

_________________________________<br />

Unterschrift<br />

Matrikel-Nr.<br />

Informatik<br />

Studiengang<br />

Fachhochschule Aachen Fachbereich Elektrotechnik und Informationstechnik<br />

Prof. Dr.-<strong>Ing</strong>. F. Wosnitza<br />

Prof. Dr.-<strong>Ing</strong>. H. <strong>Heuermann</strong><br />

5522 - DIGITALTECHNIK UND TECHNISCHE INFORMATIK<br />

Mo., 12. Juli <strong>20</strong>04 - 8:30 bis 11:30 Uhr<br />

• Es sind keine Hilfsmittel zugelassen (außer Taschenrechner mit einzeiligem<br />

Display und ohne Textspeicher).<br />

• Sämtliche Kommunikationsmittel sind verboten.<br />

• Es darf nur das ausgeteilte Papier verwendet werden.<br />

• Schreiben Sie auf jedes Blatt Ihren Namen und Ihre Matrikelnummer.<br />

• Ergebnisse, deren Lösungswege nicht aus der Darstellung ersichtlich sind<br />

oder die unleserlich sind, werden nicht gewertet.<br />

Aufgabe max.Pkt.<br />

1 25<br />

2 10<br />

3 15<br />

4 <strong>20</strong><br />

5 <strong>20</strong><br />

6 <strong>20</strong><br />

7 <strong>20</strong><br />

8 <strong>20</strong><br />

Summe<br />

150<br />

<strong>Punkte</strong><br />

Note:

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 2<br />

------------------------------------------------ -------------------------<br />

Aufgabe 1: Gegeben sei eine Signalquelle S (ρ ) mit N = 4 gleichwahrscheinlich auftrete nden<br />

Symbolen S = { s 0<br />

,...,s 3<br />

} mit p( si<br />

) = prob{ S = si} ∀ i ∈[ 0,...,3]<br />

. Die Symbole seien<br />

dualkodiert und sollen über einen gestörten Kanal übertragen werden. Das Kanalmodell ist<br />

in Abb.1.1 skizziert. Die Störquelle N ρ ) besitze folgende Einfachfe hler-<br />

Wahrscheinlichkeit, bezogen auf ein übertragenes Codewort CW( ρ k<br />

) von:<br />

p( n 0<br />

) prob N(<br />

ρ ) = 0 = 0, und p( n 1<br />

) prob{ N(<br />

ρ ) = 1} = 01,<br />

.<br />

=<br />

k<br />

{ } 9<br />

( k<br />

=<br />

k<br />

Abb. 1.1: Datenmodell des gestörten Übertragungskanals<br />

a) Bestimmen Sie die Entropie H (S)<br />

der diskreten Datenquelle S . Wie viele Bit benötigt man zum<br />

Übertragen eines Ereignisses, wie groß ist die mittlere Codewortlänge m (S)<br />

und die relative Redundanz<br />

r (S) ? Wie groß ist die Mindest-Hammingdistanz d (S ) , die Fehlererkennbarkeit F e<br />

(S)<br />

und<br />

Fehlerkorrigierbarkeit F k<br />

(S)<br />

des dualkodierten Codealphabets CW<br />

S(ρ)<br />

? Mittels des Parallel-Seriell-<br />

Schieberegisters werden gemäß Abb. 1.1 die Codeworte bitseriell über den Datenkanal übertragen.<br />

Berechnen Sie die Verbundwahrscheinlichkeits-Matrix [ p ( S,<br />

Y)<br />

] der gestörten Datenübertragungsstrecke.<br />

Wie groß ist die Verbundentropie H ( S,<br />

Y ) , die Entropie des Signals H (Y ) , die Irrelevanz H ( Y / S)<br />

, die<br />

Äquivokation H ( S / Y ) und die Transinformation TR( S → Y ) .<br />

b) Zur Erhöhung der Transinformation wird im Sender gemäß Abb. 1.2 eine Parity-Bit-Codierung auf gerades<br />

Hamming-Gewicht durchgeführt. Hierzu wird jedem Codewort (ρ )<br />

p ( ρ)<br />

∈ 0,1<br />

CW ein Parity-Bit [ ]<br />

zugefügt. Das entstehende Codealphabet X (ρ)<br />

besitzt somit gültige und ungültige Codeworte.<br />

Vervollständigen Sie die untenstehende Tabelle der gültigen Codeworte X (ρ)<br />

.<br />

S i<br />

S (ρ) CW ( ρ ) p (ρ)<br />

CW (ρ ) X<br />

Wie groß ist die Mindest-Hammingdistanz d (X ) , die Fehlererkennbarkeit F e<br />

(X ) und<br />

Fehlerkorrigierbarkeit F k<br />

(X ) des Codealphabets CW<br />

X<br />

(ρ)<br />

? Die Party-Bit-Codierten Datenworte X (ρ)<br />

werden nun über den gestörten Kanal übertragen. Berechnen Sie die Verbundwahrscheinlichkeitsmatrix<br />

[ p ( X, Y )]<br />

, die Verbundentropie H ( X , Y ) , die Irrelevanz H ( Y / X ) , die Äquivokation H ( X / Y ) und die<br />

Transinformation TR( X → Y ) des Kanals.<br />

Um wie viel Prozent hat sich die Transinformation gegenüber der uncodierten Datenübertragung verbessert?<br />

s<br />

s<br />

s<br />

0<br />

1<br />

2<br />

s<br />

3<br />

S<br />

S<br />

X<br />

S

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 3<br />

------------------------------------------------ -------------------------<br />

Aufgabe 2:<br />

Gegeben sei das untenstehende logische Schaltnetz, zu dem eine Pfadsensibilisierung für die<br />

Eingangsvariable x 1<br />

durchgeführt werden soll.<br />

x 0<br />

x<br />

1<br />

y<br />

x 2<br />

Abb.2.1: Logisches Schaltnetz<br />

a) Berechnen Sie die Schaltgleichung und führen Sie eine Pfadsensibilisierung für die Eingangsvariable x<br />

1<br />

durch.<br />

b) Zeichnen Sie den/die sensiblen Pfad(e) farbig in die obige Schaltung ein.

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 4<br />

------------------------------------------------ -------------------------<br />

Aufgabe 3:<br />

Gegeben sei der in Abb. 3.1 skizzierte Vor/Rückwärts-Primzahlenzähler, der am Ausgang<br />

die dualkodierten Primzahlen ( 5, 7, 11, 13)<br />

ausgeben soll. Ist die Eingangsvariable<br />

x ( ρ)<br />

= 1, dann soll der Primzahlenzähler modulo vorwärts zählen ( 5 , 7,11,13)<br />

, ist die<br />

Eingangsvariable x ( ρ)<br />

= 0 , dann sollen die Primzahlen modulo rückwärts gezählt werden<br />

( ,11, 7, 5)<br />

13 . Die Startstellung des Schaltwerks liegt bei Z 0 ( ρ ) und kann jederzeit über<br />

den RESET-Eingang eingenommen werden. Die Ausgabe soll dualkodiert<br />

Y ( ρ ) = 8⋅<br />

y3 + 4⋅<br />

y2<br />

+ 2⋅<br />

y1<br />

+ 1⋅<br />

y0<br />

ausgegeben werden. Das Schaltwerk soll aus maximal<br />

zwei JK-Flipflops und beliebig viele n Logikgattern aufgebaut sein.<br />

x(ρ)<br />

Modulo-<br />

Vor/Rückwärts-<br />

Primzahlenzähler<br />

(Schaltwerk)<br />

y 0<br />

y 1<br />

y 2<br />

y 3<br />

Clk<br />

RESET<br />

Abb.3.1: Modulo Vor/Rückwärts-Primzahlenzähler<br />

a) Stellen Sie die Zustandsfolgetabelle (Automatentafel) auf und skizzieren Sie den Zustandsfolgegraphen. Wie<br />

viele innere Zustände muss der Automat unterscheiden können?<br />

b) Kann der Automat als Mealy- und/oder als Moore-Automat realisiert werden? (Begründung)<br />

c) Ermitteln Sie die Schaltgleichungen für die Folgezustände Z ( ρ +1)<br />

und bringen Sie diese auf die<br />

charakteristische Form für ein JK-Flipflop. Bestimmen Sie die Ausgabefunktion y (ρ)<br />

für einen Mealy-<br />

Automaten.<br />

d) Skizzieren Sie das Schaltwerk und kennzeichnen Sie das g ( X , Z ) - und das f ( X , Z)<br />

-Schaltnetz.

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 5<br />

------------------------------------------------ -------------------------<br />

KV-Diagramme zu Aufgabe 3:<br />

0 0<br />

0 1<br />

1 1<br />

1 0<br />

0 1 1 0<br />

0 0 1 1<br />

0 0<br />

0 1<br />

1 1<br />

1 0<br />

0 1 1 0<br />

0 0 1 1<br />

0 0<br />

0 1<br />

1 1<br />

1 0<br />

0 1 1 0<br />

0 0 1 1<br />

0 0<br />

0 1<br />

1 1<br />

1 0<br />

0 1 1 0<br />

0 0 1 1<br />

0 0<br />

0 1<br />

1 1<br />

1 0<br />

0 1 1 0<br />

0 0 1 1<br />

0 0<br />

0 1<br />

1 1<br />

1 0<br />

0 1 1 0<br />

0 0 1 1<br />

0 0<br />

0 1<br />

1 1<br />

1 0<br />

0 1 1 0<br />

0 0 1 1<br />

0 0<br />

0 1<br />

1 1<br />

1 0<br />

0 1 1 0<br />

0 0 1 1

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 6<br />

------------------------------------------------ -------------------------<br />

Aufg. 4: Rückgekoppeltes Schieberegister (<strong>20</strong> <strong>Punkte</strong>)<br />

Gegeben sei das in Abb.1 skizzierte Schaltwerk mit den Ausgängen A(ρ), B(ρ), C(ρ) und D(ρ) und<br />

einem Takteingang Clk. Der innere Schaltungsaufbau des Schaltwerkes ist in Abb. 2 wiedergegeben. Es<br />

besteht aus 3 negativ-taktflankengesteuerten D-Flip-Flops sowie einem zu entwerfenden Schaltnetz f.<br />

Schaltwerk<br />

A(ρ)<br />

B(ρ)<br />

C(ρ)<br />

D(ρ)<br />

Abb. 1: Schaltwerk mit den Ausgangsvariablen A(r); B(r), C(r) und D(r).<br />

Clk<br />

f<br />

A(ρ) B(ρ) C(ρ) D(ρ)<br />

Clk<br />

Abb.2: Innerer Schaltungsaufbau des Automaten<br />

Als Zustand nach dem ? Taktimpuls bezeichnen wir die Zahl<br />

Z(ρ) = 4 A(ρ) + 2 B(ρ) + C(ρ)<br />

Mit Z(ρ)={A(ρ), B(ρ), C(ρ)} wird nach ? Taktimpulsen, mit D(ρ) wird der Ausgang des Schaltnetzes<br />

f(A,C) nach ρ Taktimpulsen bezeichnet. Ausgehend vom Zustand Z 5 =(A=1,B=0,C=1) durchläuft das<br />

Schaltwerk die folgenden Zustände in der gemäß der Zustandsfolgetabelle angegebenen Reihenfolge.

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 7<br />

------------------------------------------------ -------------------------<br />

n Z( ρ) A( ρ) B(ρ) C(ρ) Z( ρ+1) D(ρ)<br />

0 5 1 0 1<br />

1 2 0 1 0<br />

2 1 0 0 1<br />

3 4 1 0 0<br />

4 6 1 1 0<br />

5<br />

6<br />

7<br />

8<br />

a) Tragen Sie für ρ=0 bis ρ=3 jeweils die Werte für D(ρ) ein!<br />

b) Wie ist das Schaltnetz f(A,C) aufgebaut?<br />

Füllen Sie dazu die folgende Wertetabelle aus.<br />

A C D<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

c) Skizzieren Sie das Schaltnetz f(A,C). Benutzen Sie nur 2 fach NAND Gatter.<br />

d) Füllen Sie die Wahrheitstabelle für die restlichen Takte ρ=5 bis ρ=8 aus.<br />

e) Kann das Schaltwerk Zustände annehmen, die in der obigen Tabelle nicht aufgeführt<br />

sind? Benennen Sie diese.<br />

f) Im folgenden Diagramm ist für jeden Zustand ein Kreis dargestellt. Von jedem Kreis (d.h.<br />

Zustand Z(ρ)) aus zeichne man einen Pfeil zu dem folgenden Kreis (Folgezustand Z(ρ+1)).

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 8<br />

------------------------------------------------ -------------------------<br />

0 1 2 3<br />

4 5 6 7<br />

g) Wenn Sie den Zustand Z(ρ) nach dem ρ –ten Taktimpuls kennen, können Sie daraus immer<br />

ableiten, in welchem Zustand Z(ρ-1) das Schaltwerk vor dem Taktimpuls war. Für jeden Zustand<br />

gebe man an, ob dies geht oder nicht (Begründung) !<br />

h) Das Schaltwerk wird im Zustand Z 5 =(A=1,B=0,C=1) gestartet. Zeichen Sie im untenstehenden<br />

Diagramm den zeitlichen Verlauf der Signale A, B und C ein.<br />

Clk<br />

A<br />

B<br />

C<br />

t

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 9<br />

------------------------------------------------ -------------------------<br />

Aufg. 5 (<strong>20</strong> <strong>Punkte</strong>)<br />

Moderne Digital- und Mikroprozessorschaltungen verwenden „Clock“-Signale zur<br />

Eliminierung von Laufzeiteffekten.<br />

Für die im Folgenden gegebene Digitalschaltung soll das Schaltverhalten einerseits<br />

als getaktete Schaltung bei ansteigender „Clock“-Flanke und andererseits als<br />

klassische Logikschaltung dargestellt werden.<br />

Jedes Gatter hat eine Verzögerungszeit von 10ns.<br />

Die Eingangssignale A und B sowie das Clock-Signal C und die Startwerte der<br />

inneren Größen X1 und X1’ sowie der Ausgänge S und S’ sind gegeben.<br />

a) Tragen Sie das Schaltverhalten über der Zeit für X1 und S im Falle einer<br />

synchronen Schaltungsrealisierung mit Clock-Signal ein.<br />

b) Tragen Sie das Schaltverhalten über der Zeit für X1’ und S’ im Falle einer<br />

asynchronen Schaltungsrealisierung ohne Clock-Signal ein.<br />

c) Welche Clock-Frequenz hat die Schaltung?<br />

d) Welchen Vorteil haben synchrone Schaltungen gegenüber asychronen sofern<br />

die Clock-Zeiten größer als die Gatterlaufzeiten sind?

Zu Aufg. 5:<br />

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 10<br />

------------------------------------------------ -------------------------

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 11<br />

------------------------------------------------ -------------------------<br />

Aufg. 6 (<strong>20</strong> <strong>Punkte</strong>)<br />

Eine Logikschaltung mit den beiden Eingängen U A und U B und dem Ausgang Uout<br />

wird mit der Vorsorgungsspannung Vcc=2V betrieben. Die Schaltung ist aus<br />

Widerständen und spannungsgesteuerten Schaltern aufgebaut.<br />

Sofern die Steuerspannung am Schalter kleiner als Vcc/4 (gemessen gegen Masse)<br />

ist der Schalter nichtleitend. Liegt die Steuerspannung über Vcc*3/4, so ist der<br />

Schalter leitend. Die Zwischenzustände sind nicht definiert (anzugeben mit n.d.).<br />

Jeder Schalter Si weist einen Serienwiderstand Ri auf, (i=1,2,3).

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 12<br />

------------------------------------------------ -------------------------<br />

Zu Aufg. 6:<br />

a) Welcher Zusammenhang besteht zwischen den Strömen I 1 und I 4 ?<br />

b) Tragen Sie für alle vier Logikzustände und die Werte der gesuchten<br />

Spannungen und Ströme in der folgenden Tabelle ein! Die Widerstände R 1 -R 3<br />

weisen die Werte von 100W auf und R 4 und R 5 haben jeweils den Wert von<br />

1kW. Der Ausgang soll unbelastet sein.<br />

U A<br />

U B<br />

I 4<br />

I 5<br />

U S3<br />

Uout<br />

in V<br />

in V<br />

in mA<br />

in mA<br />

in V<br />

in V<br />

0 0<br />

0 2<br />

2 0<br />

2 2<br />

c) Welche logische Funktion realisiert das gegeben Schaltwerk?<br />

d) Welche Leistung wird maximal in R 4 umgesetzt?<br />

e) Wie groß dürfen R 1 und R 2 maximal sein, damit die Schaltung noch einwandfrei<br />

arbeitet? Es gilt: R= R 1 =R 2<br />

f) Welchen Nachteil hat diese Schaltungen gegenüber einer CMOS-Schaltung<br />

(insbesondere im statischen Zustand)?<br />

g) Geben Sie ein C²MOS-Schaltung an, die die gleiche Funktion hat wie die<br />

gegebene Schaltung.

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 13<br />

------------------------------------------------ -------------------------<br />

Aufg. 7 (<strong>20</strong> <strong>Punkte</strong>)<br />

Gegeben ist die folgende Innenbeschaltung eines CMOS-Gatters aus idealen P-<br />

und N-MOS Transistoren mit den Eingängen U und V, dem internen Punkt X und<br />

dem Ausgang Y. Die Schaltung wird mit Vcc=4V betrieben und alle Transistoren<br />

haben die Schaltschwelle von 2V.<br />

a) Vervollständigen Sie die folgende Tabelle. Zustände mit Spannungen >2V<br />

werden mit einer logischen 1 und Zustände mit Spannungen

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 14<br />

------------------------------------------------ -------------------------<br />

Zu Aufg. 7:<br />

Gegeben ist nun eine CMOS-Schaltung nach dem folgenden Bild mit gleichen<br />

Transistoren und gleichen Logikzuständen und –pegeln. Getaktet wird die<br />

Schaltung über das Signal Clock1 (kurz C 1 ).<br />

c) Gegeben Sie die inneren Logikzustände L und X sowie den Logikzustand am<br />

Ausgang (Out) über der Zeit im folgenden Diagramm in Abhängigkeit des<br />

Eingangssignals (In) und des Clock-Signals an.<br />

d) Wie bezeichnet man diese Schaltung?

DTTI – S04.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 15<br />

------------------------------------------------ -------------------------<br />

Aufg. 8 (<strong>20</strong> <strong>Punkte</strong>)<br />

a) Für welches Bauelement lässt sich der Wert <strong>20</strong> fF angeben? Was bedeutet<br />

fF?<br />

b) Wie wird aus dem Strom I und der Spannung U die elektrische Leistung P<br />

berechnet?<br />

c) Die Stromversorgungsleitung zwischen Schaltnetzteil und CPU hat einen<br />

elektrischen Widerstand von 50mW. Welche Spannung U netz muss das<br />

Schaltnetzteil liefern, damit an der CPU 2.9V bei einem Stromfluss von 1.8A<br />

anliegen?<br />

d) Ein Treiber für eine Datenleitung nimmt bei einer Versorgungsspannung von<br />

1V eine Leistung von 10mW auf und kann einen Strom von 10mA bei einem<br />

High-Signal von 0.8V treiben. Wie groß ist der Wirkungsgrad h des Treibers?<br />

e) Skizzieren Sie den prinzipiellen Aufbau einer Gatterschaltung in C²MOS-<br />

Technik!<br />

f) Wofür steht die Ankürzung CMOS?<br />

g) Skizzieren Sie das dynamische D-Flipflop mit einem CMOS-Transistor!<br />

h) Welche Arten von nicht flüchtigen Speichern gibt es? Es genügt die Angabe<br />

der abgekürzten Namen.<br />

i) Wozu verwendet man Dekoder in Speicherbausteinen?<br />

j) Geben Sie das Schaltbild der 1-Transistorzelle einer DRAM-Speichereinheit<br />

mit den Anschlüssen BL und WL an.<br />

k) Welche digitalen Speichermedien verwenden sogenannte Pits zur<br />

Datenspeicherung? Die Angabe der Abkürzungen genügt.<br />

l) Welcher Widerstandswert wird im LVDS-Standard zur Realisierung der<br />

Wellenwiderstände der differentiellen Übertragungsleitungen und der<br />

Terminierungen eingesetzt?<br />

m) Illustrieren Sie wie ein typisches Augendiagramm einschließlich einer Maske<br />

zur Durchführung eines BER-Test aussieht.