Flash-basierte FPGAs (1)

Flash-basierte FPGAs (1)

Flash-basierte FPGAs (1)

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

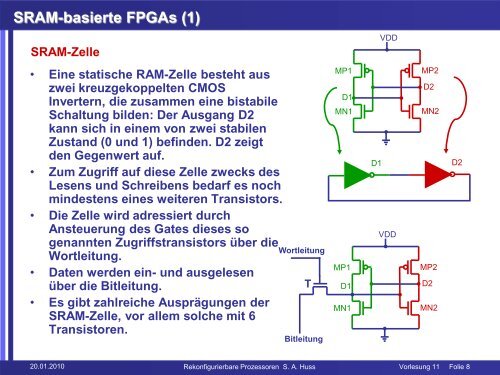

SRAM-<strong>basierte</strong> <strong>FPGAs</strong> (1)<br />

SRAM-Zelle<br />

VDD<br />

• Eine statische RAM-Zelle besteht aus<br />

zwei kreuzgekoppelten CMOS<br />

Invertern, die zusammen eine bistabile<br />

Schaltung bilden: Der Ausgang D2<br />

kann sich in einem von zwei stabilen<br />

Zustand (0 und 1) befinden. D2 zeigt<br />

den Gegenwert auf.<br />

• Zum Zugriff auf diese Zelle zwecks des<br />

Lesens und Schreibens bedarf es noch<br />

mindestens eines weiteren Transistors.<br />

• Die Zelle wird adressiert durch<br />

Ansteuerung des Gates dieses so<br />

genannten Zugriffstransistors über die<br />

Wortleitung.<br />

• Daten werden ein- und ausgelesen<br />

über die Bitleitung.<br />

• Es gibt zahlreiche Ausprägungen der<br />

SRAM-Zelle, vor allem solche mit 6<br />

Transistoren.<br />

Wortleitung<br />

T<br />

Bitleitung<br />

MP1<br />

D1<br />

MN1<br />

MP1<br />

D1<br />

MN1<br />

D1<br />

VDD<br />

MP2<br />

D2<br />

MN2<br />

MP2<br />

D2<br />

MN2<br />

D2<br />

20.01.2010<br />

Rekonfigurierbare Prozessoren S. A. Huss<br />

Vorlesung 11 Folie 8