Diplomarbeit - Fingers elektrische Welt

Diplomarbeit - Fingers elektrische Welt

Diplomarbeit - Fingers elektrische Welt

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

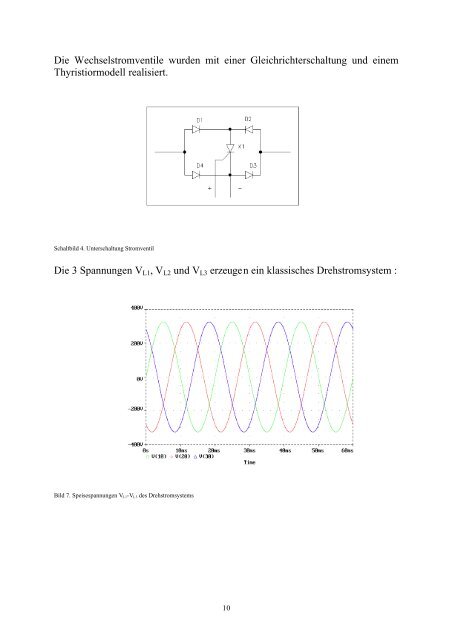

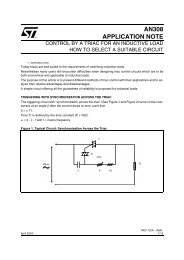

Die Wechselstromventile wurden mit einer Gleichrichterschaltung und einem<br />

Thyristiormodell realisiert.<br />

Schaltbild 4. Unterschaltung Stromventil<br />

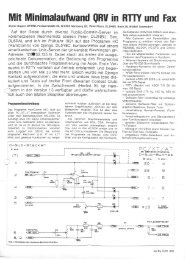

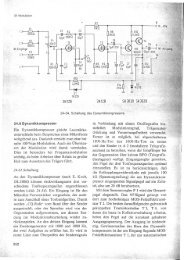

Die 3 Spannungen VL1, VL2 und VL3 erzeugen ein klassisches Drehstromsystem :<br />

Bild 7. Speisespannungen VL1-VL3 des Drehstromsystems<br />

10