Volltext (PDF) - Qucosa

Volltext (PDF) - Qucosa

Volltext (PDF) - Qucosa

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Einleitung<br />

1 Einleitung<br />

1.1 Bedeutung und Anforderung an das Planarisieren bei der Herstellung<br />

hochentwickelter integrierter Schaltkreise<br />

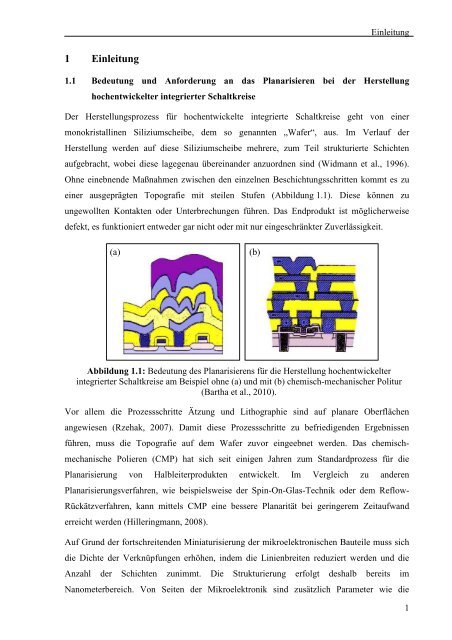

Der Herstellungsprozess für hochentwickelte integrierte Schaltkreise geht von einer<br />

monokristallinen Siliziumscheibe, dem so genannten „Wafer“, aus. Im Verlauf der<br />

Herstellung werden auf diese Siliziumscheibe mehrere, zum Teil strukturierte Schichten<br />

aufgebracht, wobei diese lagegenau übereinander anzuordnen sind (Widmann et al., 1996).<br />

Ohne einebnende Maßnahmen zwischen den einzelnen Beschichtungsschritten kommt es zu<br />

einer ausgeprägten Topografie mit steilen Stufen (Abbildung 1.1). Diese können zu<br />

ungewollten Kontakten oder Unterbrechungen führen. Das Endprodukt ist möglicherweise<br />

defekt, es funktioniert entweder gar nicht oder mit nur eingeschränkter Zuverlässigkeit.<br />

(a)<br />

(b)<br />

Abbildung 1.1: Bedeutung des Planarisierens für die Herstellung hochentwickelter<br />

integrierter Schaltkreise am Beispiel ohne (a) und mit (b) chemisch-mechanischer Politur<br />

(Bartha et al., 2010).<br />

Vor allem die Prozessschritte Ätzung und Lithographie sind auf planare Oberflächen<br />

angewiesen (Rzehak, 2007). Damit diese Prozessschritte zu befriedigenden Ergebnissen<br />

führen, muss die Topografie auf dem Wafer zuvor eingeebnet werden. Das chemischmechanische<br />

Polieren (CMP) hat sich seit einigen Jahren zum Standardprozess für die<br />

Planarisierung von Halbleiterprodukten entwickelt. Im Vergleich zu anderen<br />

Planarisierungsverfahren, wie beispielsweise der Spin-On-Glas-Technik oder dem Reflow-<br />

Rückätzverfahren, kann mittels CMP eine bessere Planarität bei geringerem Zeitaufwand<br />

erreicht werden (Hilleringmann, 2008).<br />

Auf Grund der fortschreitenden Miniaturisierung der mikroelektronischen Bauteile muss sich<br />

die Dichte der Verknüpfungen erhöhen, indem die Linienbreiten reduziert werden und die<br />

Anzahl der Schichten zunimmt. Die Strukturierung erfolgt deshalb bereits im<br />

Nanometerbereich. Von Seiten der Mikroelektronik sind zusätzlich Parameter wie die<br />

1