A Top-Down Verilog-A Design on the Analog-and-Digital

A Top-Down Verilog-A Design on the Analog-and-Digital

A Top-Down Verilog-A Design on the Analog-and-Digital

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

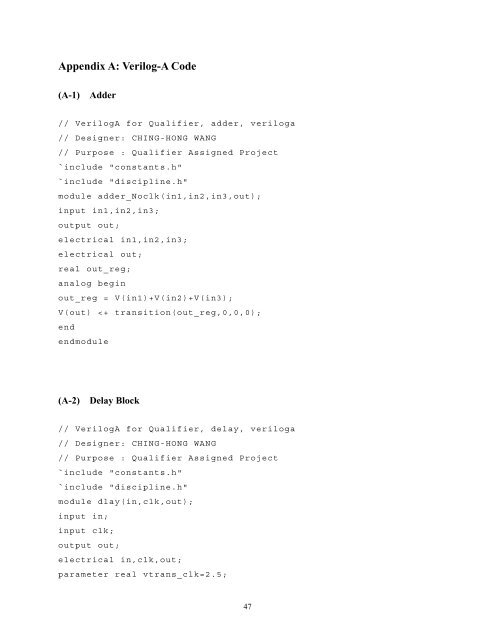

Appendix A: <str<strong>on</strong>g>Verilog</str<strong>on</strong>g>-A Code<br />

(A-1) Adder<br />

// <str<strong>on</strong>g>Verilog</str<strong>on</strong>g>A<br />

// <str<strong>on</strong>g>Design</str<strong>on</strong>g>er:<br />

for Qualifier, adder, veriloga<br />

CHING-HONG WANG<br />

// Purpose : Qualifier Assigned Project<br />

`include "c<strong>on</strong>stants.h"<br />

`include "discipline.h"<br />

module adder_Noclk(in1,in2,in3,out);<br />

input in1,in2,in3;<br />

output out;<br />

electrical in1,in2,in3;<br />

electrical out;<br />

real out_reg;<br />

analog begin<br />

out_reg = V(in1)+V(in2)+V(in3);<br />

V(out)