A Top-Down Verilog-A Design on the Analog-and-Digital

A Top-Down Verilog-A Design on the Analog-and-Digital

A Top-Down Verilog-A Design on the Analog-and-Digital

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

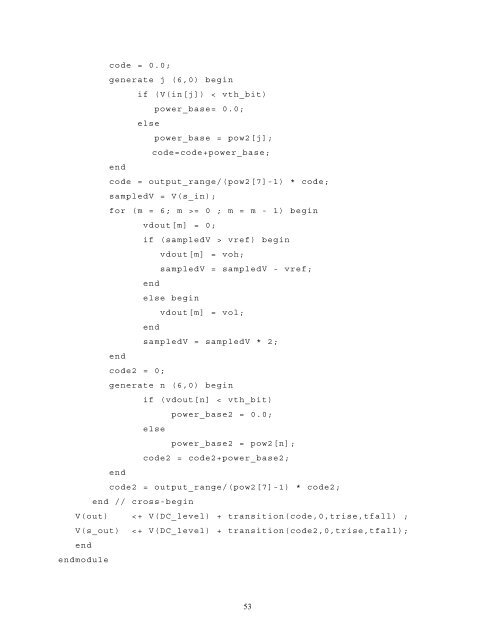

code = 0.0;<br />

generate j (6,0) begin<br />

end<br />

if (V(in[j]) < vth_bit)<br />

else<br />

power_base=<br />

0.0;<br />

power_base = pow2[j];<br />

code=code+power_base;<br />

code = output_range/(pow2[7]-1)<br />

sampledV = V(s_in);<br />

* code;<br />

for ( m = 6; m >= 0 ; m = m - 1) begin<br />

end<br />

vdout[m] = 0;<br />

if (sampledV ><br />

end<br />

vdout[m] = voh;<br />

vref) begin<br />

sampledV = sampledV<br />

- vref;<br />

else begin<br />

end<br />

code2 = 0;<br />

vdout[m] = vol;<br />

sampledV = sampledV<br />

* 2;<br />

generate n (6,0) begin<br />

end<br />

if (vdout[n] < vth_bit)<br />

else<br />

power_base2<br />

= 0.0;<br />

power_base2 = pow2[n];<br />

code2 = code2+power_base2;<br />

code2 = output_range/(pow2[7]-1) *<br />

end // cross-begin<br />

V(out)