Logic Array Blocks and Adaptive Logic Modules in Cyclone ... - Altera

Logic Array Blocks and Adaptive Logic Modules in Cyclone ... - Altera

Logic Array Blocks and Adaptive Logic Modules in Cyclone ... - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

1-10<br />

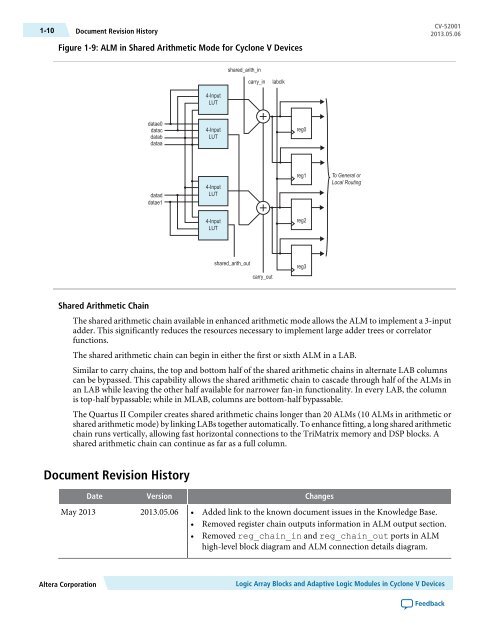

Figure 1-9: ALM <strong>in</strong> Shared Arithmetic Mode for <strong>Cyclone</strong> V Devices<br />

Shared Arithmetic Cha<strong>in</strong><br />

datae0<br />

datac<br />

datab<br />

dataa<br />

datad<br />

datae1<br />

4-Input<br />

LUT<br />

4-Input<br />

LUT<br />

4-Input<br />

LUT<br />

4-Input<br />

LUT<br />

shared_arith_<strong>in</strong><br />

shared_arith_out<br />

carry_<strong>in</strong><br />

carry_out<br />

labclk<br />

reg0<br />

reg1<br />

reg2<br />

reg3<br />

To General or<br />

Local Rout<strong>in</strong>g<br />

The shared arithmetic cha<strong>in</strong> available <strong>in</strong> enhanced arithmetic mode allows the ALM to implement a 3-<strong>in</strong>put<br />

adder. This significantly reduces the resources necessary to implement large adder trees or correlator<br />

functions.<br />

The shared arithmetic cha<strong>in</strong> can beg<strong>in</strong> <strong>in</strong> either the first or sixth ALM <strong>in</strong> a LAB.<br />

Similar to carry cha<strong>in</strong>s, the top <strong>and</strong> bottom half of the shared arithmetic cha<strong>in</strong>s <strong>in</strong> alternate LAB columns<br />

can be bypassed. This capability allows the shared arithmetic cha<strong>in</strong> to cascade through half of the ALMs <strong>in</strong><br />

an LAB while leav<strong>in</strong>g the other half available for narrower fan-<strong>in</strong> functionality. In every LAB, the column<br />

is top-half bypassable; while <strong>in</strong> MLAB, columns are bottom-half bypassable.<br />

The Quartus II Compiler creates shared arithmetic cha<strong>in</strong>s longer than 20 ALMs (10 ALMs <strong>in</strong> arithmetic or<br />

shared arithmetic mode) by l<strong>in</strong>k<strong>in</strong>g LABs together automatically. To enhance fitt<strong>in</strong>g, a long shared arithmetic<br />

cha<strong>in</strong> runs vertically, allow<strong>in</strong>g fast horizontal connections to the TriMatrix memory <strong>and</strong> DSP blocks. A<br />

shared arithmetic cha<strong>in</strong> can cont<strong>in</strong>ue as far as a full column.<br />

Document Revision History<br />

Date<br />

May 2013<br />

<strong>Altera</strong> Corporation<br />

Document Revision History<br />

Version<br />

2013.05.06<br />

Changes<br />

• Added l<strong>in</strong>k to the known document issues <strong>in</strong> the Knowledge Base.<br />

• Removed register cha<strong>in</strong> outputs <strong>in</strong>formation <strong>in</strong> ALM output section.<br />

• Removed reg_cha<strong>in</strong>_<strong>in</strong> <strong>and</strong> reg_cha<strong>in</strong>_out ports <strong>in</strong> ALM<br />

high-level block diagram <strong>and</strong> ALM connection details diagram.<br />

<strong>Logic</strong> <strong>Array</strong> <strong>Blocks</strong> <strong>and</strong> <strong>Adaptive</strong> <strong>Logic</strong> <strong>Modules</strong> <strong>in</strong> <strong>Cyclone</strong> V Devices<br />

CV-52001<br />

2013.05.06<br />

Feedback