- Page 1 and 2: Features • Utilizes the AVR ® RI

- Page 3 and 4: Block Diagram 2543K-AVR-03/10 Figur

- Page 5 and 6: Pin Descriptions VCC Digital supply

- Page 7 and 8: About Code Examples 2543K-AVR-03/10

- Page 9 and 10: AVR CPU Core 2543K-AVR-03/10 ATtiny

- Page 11 and 12: General Purpose Register File 2543K

- Page 13 and 14: 2543K-AVR-03/10 ATtiny2313 Stack Po

- Page 15 and 16: Interrupt Response Time 2543K-AVR-0

- Page 17 and 18: SRAM Data Memory Data Memory Access

- Page 19 and 20: The EEPROM Data Register - EEDR The

- Page 21 and 22: 2543K-AVR-03/10 ATtiny2313 The foll

- Page 23 and 24: General Purpose I/O Registers Gener

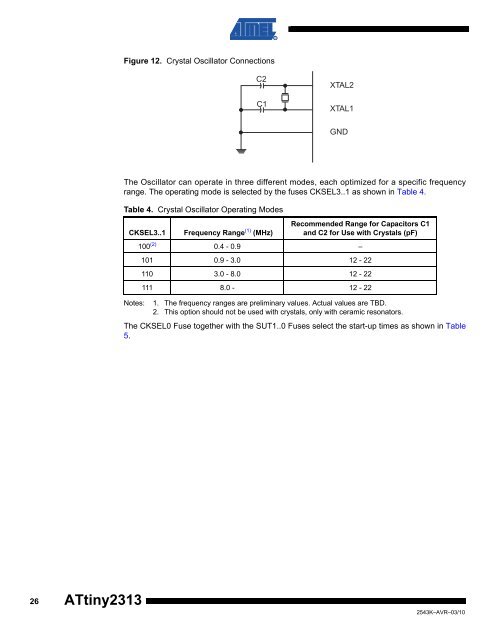

- Page 25: 2543K-AVR-03/10 ATtiny2313 Clock So

- Page 29 and 30: 2543K-AVR-03/10 ATtiny2313 External

- Page 31 and 32: 2543K-AVR-03/10 ATtiny2313 cleared

- Page 33 and 34: 2543K-AVR-03/10 ATtiny2313 Power-do

- Page 35 and 36: System Control and Reset 2543K-AVR-

- Page 37 and 38: 2543K-AVR-03/10 Figure 16. MCU Star

- Page 39 and 40: 2543K-AVR-03/10 ATtiny2313 Watchdog

- Page 41 and 42: Watchdog Timer ATtiny2313 has an En

- Page 43 and 44: 2543K-AVR-03/10 ATtiny2313 The foll

- Page 45 and 46: 2543K-AVR-03/10 Table 20. Watchdog

- Page 47 and 48: 2543K-AVR-03/10 ATtiny2313 The most

- Page 49 and 50: Ports as General Digital I/O 2543K-

- Page 51 and 52: 2543K-AVR-03/10 ATtiny2313 Consider

- Page 53 and 54: Alternate Port Functions 2543K-AVR-

- Page 55 and 56: MCU Control Register - MCUCR Altern

- Page 57 and 58: 2543K-AVR-03/10 Table 26. Overridin

- Page 59 and 60: 2543K-AVR-03/10 ATtiny2313 Table 29

- Page 61 and 62: External Interrupts Pin Change Inte

- Page 63 and 64: External Interrupt Flag Register -

- Page 65 and 66: 2543K-AVR-03/10 ATtiny2313 Definiti

- Page 67 and 68: Force Output Compare Compare Match

- Page 69 and 70: Clear Timer on Compare Match (CTC)

- Page 71 and 72: Phase Correct PWM Mode 2543K-AVR-03

- Page 73 and 74: Timer/Counter Timing Diagrams 2543K

- Page 75 and 76: 8-bit Timer/Counter Register Descri

- Page 77 and 78:

2543K-AVR-03/10 ATtiny2313 Table 39

- Page 79 and 80:

Timer/Counter Register - TCNT0 Outp

- Page 81 and 82:

2543K-AVR-03/10 ATtiny2313 the flag

- Page 83 and 84:

General Timer/Counter Control Regis

- Page 85 and 86:

2543K-AVR-03/10 ATtiny2313 Register

- Page 87 and 88:

2543K-AVR-03/10 Assembly Code Examp

- Page 89 and 90:

Reusing the Temporary High Byte Reg

- Page 91 and 92:

2543K-AVR-03/10 ATtiny2313 The Time

- Page 93 and 94:

2543K-AVR-03/10 ATtiny2313 are used

- Page 95 and 96:

Compare Match Output Unit 2543K-AVR

- Page 97 and 98:

2543K-AVR-03/10 Figure 45. CTC Mode

- Page 99 and 100:

2543K-AVR-03/10 ATtiny2313 Note tha

- Page 101 and 102:

2543K-AVR-03/10 ATtiny2313 value (a

- Page 103 and 104:

2543K-AVR-03/10 ATtiny2313 The Time

- Page 105 and 106:

2543K-AVR-03/10 Figure 51. Timer/Co

- Page 107 and 108:

2543K-AVR-03/10 ATtiny2313 Note: 1.

- Page 109 and 110:

Timer/Counter1 Control Register B -

- Page 111 and 112:

Output Compare Register 1 B - OCR1B

- Page 113 and 114:

2543K-AVR-03/10 ATtiny2313 USART Th

- Page 115 and 116:

Internal Clock Generation - The Bau

- Page 117 and 118:

2543K-AVR-03/10 ATtiny2313 ing XCK

- Page 119 and 120:

2543K-AVR-03/10 ATtiny2313 More adv

- Page 121 and 122:

Sending Frames with 9 Data Bit 2543

- Page 123 and 124:

Data Reception - The USART Receiver

- Page 125 and 126:

Receive Compete Flag and Interrupt

- Page 127 and 128:

Asynchronous Clock Recovery Asynchr

- Page 129 and 130:

2543K-AVR-03/10 ATtiny2313 Table 49

- Page 131 and 132:

USART Register Description USART I/

- Page 133 and 134:

USART Control and Status Register B

- Page 135 and 136:

USART Baud Rate Registers - UBRRL a

- Page 137 and 138:

Table 57. Examples of UBRR Settings

- Page 139 and 140:

2543K-AVR-03/10 Table 59. Examples

- Page 141 and 142:

Functional Descriptions 2543K-AVR-0

- Page 143 and 144:

SPI Slave Operation Example 2543K-A

- Page 145 and 146:

2543K-AVR-03/10 Figure 64. Two-wire

- Page 147 and 148:

USI Status Register - USISR USI Con

- Page 149 and 150:

2543K-AVR-03/10 Table 60. Relations

- Page 151 and 152:

Analog Comparator Analog Comparator

- Page 153 and 154:

debugWIRE Onchip Debug System 2543K

- Page 155 and 156:

Self- Programming the Flash Perform

- Page 157 and 158:

Store Program Memory Control and St

- Page 159 and 160:

Preventing Flash Corruption Program

- Page 161 and 162:

2543K-AVR-03/10 ATtiny2313 Fuse Bit

- Page 163 and 164:

Parallel Programming Parameters, Pi

- Page 165 and 166:

Serial Programming Pin Mapping Para

- Page 167 and 168:

Programming the Flash 2543K-AVR-03/

- Page 169 and 170:

Programming the EEPROM 2543K-AVR-03

- Page 171 and 172:

Programming the Lock Bits Reading t

- Page 173 and 174:

2543K-AVR-03/10 ATtiny2313 Figure 7

- Page 175 and 176:

Serial Programming Algorithm 2543K-

- Page 177 and 178:

Table 78. Serial Programming Instru

- Page 179 and 180:

Electrical Characteristics Absolute

- Page 181 and 182:

External Clock Drive Waveforms Exte

- Page 183 and 184:

ATtiny2313 Typical Characteristics

- Page 185 and 186:

2543K-AVR-03/10 Figure 87. Active S

- Page 187 and 188:

Idle Supply Current Figure 91. Idle

- Page 189 and 190:

2543K-AVR-03/10 Figure 95. Idle Sup

- Page 191 and 192:

Standby Supply Current 2543K-AVR-03

- Page 193 and 194:

2543K-AVR-03/10 Figure 103. Reset P

- Page 195 and 196:

2543K-AVR-03/10 Figure 107. I/O Pin

- Page 197 and 198:

2543K-AVR-03/10 Figure 111. Reset I

- Page 199 and 200:

2543K-AVR-03/10 Figure 115. Reset I

- Page 201 and 202:

2543K-AVR-03/10 Figure 119. Reset I

- Page 203 and 204:

2543K-AVR-03/10 Figure 123. Reset I

- Page 205 and 206:

Internal Oscillator Speed 2543K-AVR

- Page 207 and 208:

2543K-AVR-03/10 Figure 131. Calibra

- Page 209 and 210:

Current Consumption of Peripheral U

- Page 211 and 212:

Current Consumption in Reset and Re

- Page 213 and 214:

Register Summary 2543K-AVR-03/10 AT

- Page 215 and 216:

Instruction Set Summary 2543K-AVR-0

- Page 217 and 218:

Ordering Information Speed (MHz) (3

- Page 219 and 220:

20S 2543K-AVR-03/10 ATtiny2313 219

- Page 221 and 222:

Errata The revision in this section

- Page 223 and 224:

Changes from Rev. 2514F-08/04 to Re

- Page 225 and 226:

Table of Contents 2543K-AVR-03/10 F

- Page 227 and 228:

2543K-AVR-03/10 Limitations of debu