Chapter 02 Memory Mapping.pdf

Chapter 02 Memory Mapping.pdf

Chapter 02 Memory Mapping.pdf

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Public Version<br />

L3 and L4 <strong>Memory</strong> Space <strong>Mapping</strong> www.ti.com<br />

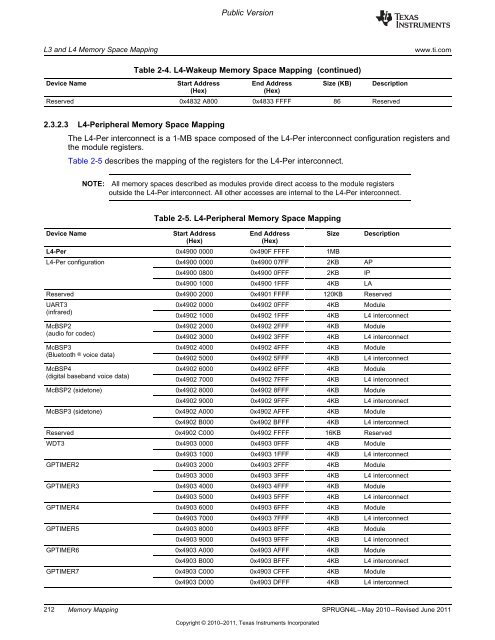

Table 2-4. L4-Wakeup <strong>Memory</strong> Space <strong>Mapping</strong> (continued)<br />

Device Name Start Address End Address Size (KB) Description<br />

(Hex) (Hex)<br />

Reserved 0x4832 A800 0x4833 FFFF 86 Reserved<br />

2.3.2.3 L4-Peripheral <strong>Memory</strong> Space <strong>Mapping</strong><br />

The L4-Per interconnect is a 1-MB space composed of the L4-Per interconnect configuration registers and<br />

the module registers.<br />

Table 2-5 describes the mapping of the registers for the L4-Per interconnect.<br />

NOTE: All memory spaces described as modules provide direct access to the module registers<br />

outside the L4-Per interconnect. All other accesses are internal to the L4-Per interconnect.<br />

Table 2-5. L4-Peripheral <strong>Memory</strong> Space <strong>Mapping</strong><br />

Device Name Start Address End Address Size Description<br />

(Hex) (Hex)<br />

L4-Per 0x4900 0000 0x490F FFFF 1MB<br />

L4-Per configuration 0x4900 0000 0x4900 07FF 2KB AP<br />

0x4900 0800 0x4900 0FFF 2KB IP<br />

0x4900 1000 0x4900 1FFF 4KB LA<br />

Reserved 0x4900 2000 0x4901 FFFF 120KB Reserved<br />

UART3 0x49<strong>02</strong> 0000 0x49<strong>02</strong> 0FFF 4KB Module<br />

(infrared)<br />

0x49<strong>02</strong> 1000 0x49<strong>02</strong> 1FFF 4KB L4 interconnect<br />

McBSP2 0x49<strong>02</strong> 2000 0x49<strong>02</strong> 2FFF 4KB Module<br />

(audio for codec)<br />

0x49<strong>02</strong> 3000 0x49<strong>02</strong> 3FFF 4KB L4 interconnect<br />

McBSP3 0x49<strong>02</strong> 4000 0x49<strong>02</strong> 4FFF 4KB Module<br />

(Bluetooth ® voice data)<br />

0x49<strong>02</strong> 5000 0x49<strong>02</strong> 5FFF 4KB L4 interconnect<br />

McBSP4 0x49<strong>02</strong> 6000 0x49<strong>02</strong> 6FFF 4KB Module<br />

(digital baseband voice data)<br />

0x49<strong>02</strong> 7000 0x49<strong>02</strong> 7FFF 4KB L4 interconnect<br />

McBSP2 (sidetone) 0x49<strong>02</strong> 8000 0x49<strong>02</strong> 8FFF 4KB Module<br />

0x49<strong>02</strong> 9000 0x49<strong>02</strong> 9FFF 4KB L4 interconnect<br />

McBSP3 (sidetone) 0x49<strong>02</strong> A000 0x49<strong>02</strong> AFFF 4KB Module<br />

0x49<strong>02</strong> B000 0x49<strong>02</strong> BFFF 4KB L4 interconnect<br />

Reserved 0x49<strong>02</strong> C000 0x49<strong>02</strong> FFFF 16KB Reserved<br />

WDT3 0x4903 0000 0x4903 0FFF 4KB Module<br />

0x4903 1000 0x4903 1FFF 4KB L4 interconnect<br />

GPTIMER2 0x4903 2000 0x4903 2FFF 4KB Module<br />

0x4903 3000 0x4903 3FFF 4KB L4 interconnect<br />

GPTIMER3 0x4903 4000 0x4903 4FFF 4KB Module<br />

0x4903 5000 0x4903 5FFF 4KB L4 interconnect<br />

GPTIMER4 0x4903 6000 0x4903 6FFF 4KB Module<br />

0x4903 7000 0x4903 7FFF 4KB L4 interconnect<br />

GPTIMER5 0x4903 8000 0x4903 8FFF 4KB Module<br />

0x4903 9000 0x4903 9FFF 4KB L4 interconnect<br />

GPTIMER6 0x4903 A000 0x4903 AFFF 4KB Module<br />

0x4903 B000 0x4903 BFFF 4KB L4 interconnect<br />

GPTIMER7 0x4903 C000 0x4903 CFFF 4KB Module<br />

0x4903 D000 0x4903 DFFF 4KB L4 interconnect<br />

212 <strong>Memory</strong> <strong>Mapping</strong> SPRUGN4L–May 2010–Revised June 2011<br />

Copyright © 2010–2011, Texas Instruments Incorporated