Chapter 02 Memory Mapping.pdf

Chapter 02 Memory Mapping.pdf

Chapter 02 Memory Mapping.pdf

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Public Version<br />

L3 and L4 <strong>Memory</strong> Space <strong>Mapping</strong> www.ti.com<br />

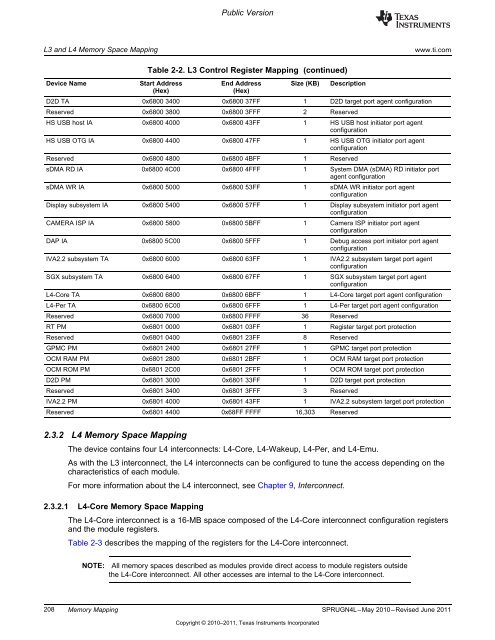

Table 2-2. L3 Control Register <strong>Mapping</strong> (continued)<br />

Device Name Start Address End Address Size (KB) Description<br />

(Hex) (Hex)<br />

D2D TA 0x6800 3400 0x6800 37FF 1 D2D target port agent configuration<br />

Reserved 0x6800 3800 0x6800 3FFF 2 Reserved<br />

HS USB host IA 0x6800 4000 0x6800 43FF 1 HS USB host initiator port agent<br />

configuration<br />

HS USB OTG IA 0x6800 4400 0x6800 47FF 1 HS USB OTG initiator port agent<br />

configuration<br />

Reserved 0x6800 4800 0x6800 4BFF 1 Reserved<br />

sDMA RD IA 0x6800 4C00 0x6800 4FFF 1 System DMA (sDMA) RD initiator port<br />

agent configuration<br />

sDMA WR IA 0x6800 5000 0x6800 53FF 1 sDMA WR initiator port agent<br />

configuration<br />

Display subsystem IA 0x6800 5400 0x6800 57FF 1 Display subsystem initiator port agent<br />

configuration<br />

CAMERA ISP IA 0x6800 5800 0x6800 5BFF 1 Camera ISP initiator port agent<br />

configuration<br />

DAP IA 0x6800 5C00 0x6800 5FFF 1 Debug access port initiator port agent<br />

configuration<br />

IVA2.2 subsystem TA 0x6800 6000 0x6800 63FF 1 IVA2.2 subsystem target port agent<br />

configuration<br />

SGX subsystem TA 0x6800 6400 0x6800 67FF 1 SGX subsystem target port agent<br />

configuration<br />

L4-Core TA 0x6800 6800 0x6800 6BFF 1 L4-Core target port agent configuration<br />

L4-Per TA 0x6800 6C00 0x6800 6FFF 1 L4-Per target port agent configuration<br />

Reserved 0x6800 7000 0x6800 FFFF 36 Reserved<br />

RT PM 0x6801 0000 0x6801 03FF 1 Register target port protection<br />

Reserved 0x6801 0400 0x6801 23FF 8 Reserved<br />

GPMC PM 0x6801 2400 0x6801 27FF 1 GPMC target port protection<br />

OCM RAM PM 0x6801 2800 0x6801 2BFF 1 OCM RAM target port protection<br />

OCM ROM PM 0x6801 2C00 0x6801 2FFF 1 OCM ROM target port protection<br />

D2D PM 0x6801 3000 0x6801 33FF 1 D2D target port protection<br />

Reserved 0x6801 3400 0x6801 3FFF 3 Reserved<br />

IVA2.2 PM 0x6801 4000 0x6801 43FF 1 IVA2.2 subsystem target port protection<br />

Reserved 0x6801 4400 0x68FF FFFF 16,303 Reserved<br />

2.3.2 L4 <strong>Memory</strong> Space <strong>Mapping</strong><br />

The device contains four L4 interconnects: L4-Core, L4-Wakeup, L4-Per, and L4-Emu.<br />

As with the L3 interconnect, the L4 interconnects can be configured to tune the access depending on the<br />

characteristics of each module.<br />

For more information about the L4 interconnect, see <strong>Chapter</strong> 9, Interconnect.<br />

2.3.2.1 L4-Core <strong>Memory</strong> Space <strong>Mapping</strong><br />

The L4-Core interconnect is a 16-MB space composed of the L4-Core interconnect configuration registers<br />

and the module registers.<br />

Table 2-3 describes the mapping of the registers for the L4-Core interconnect.<br />

NOTE: All memory spaces described as modules provide direct access to module registers outside<br />

the L4-Core interconnect. All other accesses are internal to the L4-Core interconnect.<br />

208 <strong>Memory</strong> <strong>Mapping</strong> SPRUGN4L–May 2010–Revised June 2011<br />

Copyright © 2010–2011, Texas Instruments Incorporated