FPGA Based Network Security architecture for High Speed Networks

FPGA Based Network Security architecture for High Speed Networks

FPGA Based Network Security architecture for High Speed Networks

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

4.3 Result and comparison with other schemes<br />

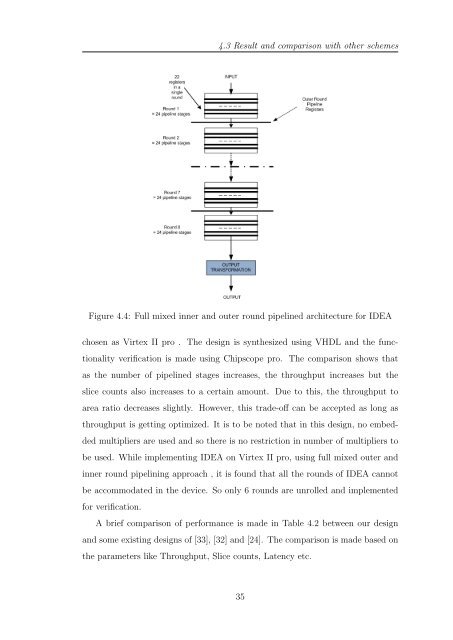

Figure 4.4: Full mixed inner and outer round pipelined <strong>architecture</strong> <strong>for</strong> IDEA<br />

chosen as Virtex II pro . The design is synthesized using VHDL and the func-<br />

tionality verification is made using Chipscope pro. The comparison shows that<br />

as the number of pipelined stages increases, the throughput increases but the<br />

slice counts also increases to a certain amount. Due to this, the throughput to<br />

area ratio decreases slightly. However, this trade-off can be accepted as long as<br />

throughput is getting optimized. It is to be noted that in this design, no embed-<br />

ded multipliers are used and so there is no restriction in number of multipliers to<br />

be used. While implementing IDEA on Virtex II pro, using full mixed outer and<br />

inner round pipelining approach , it is found that all the rounds of IDEA cannot<br />

be accommodated in the device. So only 6 rounds are unrolled and implemented<br />

<strong>for</strong> verification.<br />

A brief comparison of per<strong>for</strong>mance is made in Table 4.2 between our design<br />

and some existing designs of [33], [32] and [24]. The comparison is made based on<br />

the parameters like Throughput, Slice counts, Latency etc.<br />

35