On-chip Networks for Manycore Architecture Myong ... - People - MIT

On-chip Networks for Manycore Architecture Myong ... - People - MIT

On-chip Networks for Manycore Architecture Myong ... - People - MIT

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

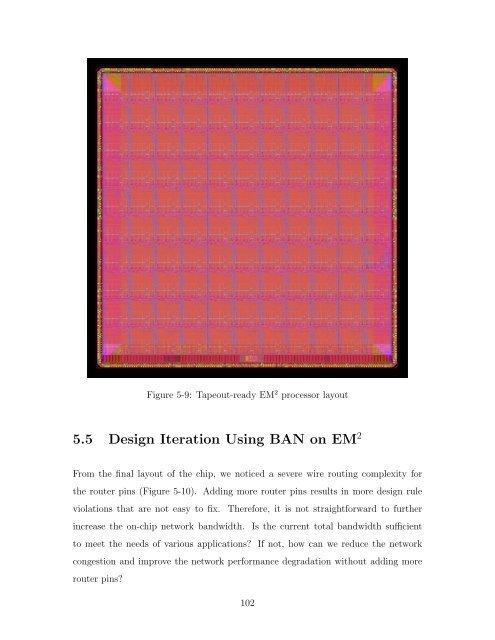

Figure 5-9: Tapeout-ready EM 2 processor layout<br />

5.5 Design Iteration Using BAN on EM 2<br />

From the final layout of the <strong>chip</strong>, we noticed a severe wire routing complexity <strong>for</strong><br />

the router pins (Figure 5-10). Adding more router pins results in more design rule<br />

violations that are not easy to fix. There<strong>for</strong>e, it is not straight<strong>for</strong>ward to further<br />

increase the on-<strong>chip</strong> network bandwidth. Is the current total bandwidth su cient<br />

to meet the needs of various applications? If not, how can we reduce the network<br />

congestion and improve the network per<strong>for</strong>mance degradation without adding more<br />

router pins?<br />

102