Spectral Estimation Using a MUSIC Algorithm - Altera

Spectral Estimation Using a MUSIC Algorithm - Altera

Spectral Estimation Using a MUSIC Algorithm - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Nios II Embedded Processor Design Contest—Outstanding Designs 2005<br />

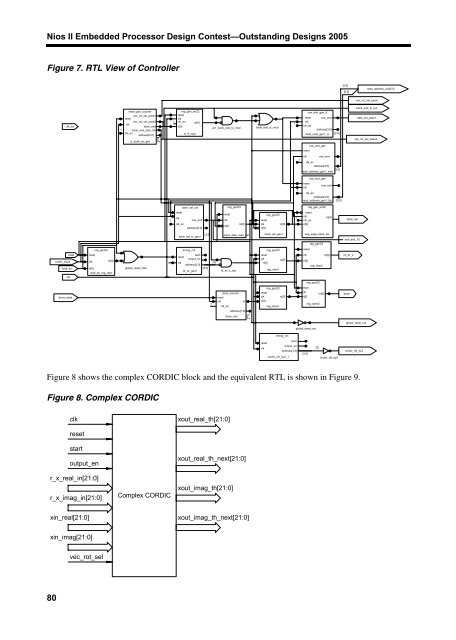

Figure 7. RTL View of Controller<br />

[2:0]<br />

[2:0]<br />

read_address_out[5:0]<br />

vec_rot_sel_pass1<br />

clk_en<br />

reset_gen_counter<br />

vec_rot_sel_pass1<br />

reset<br />

vec_rot_sel_pass2<br />

clk<br />

bank_end<br />

1 bank_end_rdwr_dis<br />

clk_en<br />

address[4:0]<br />

reg_gen_enZ2<br />

reset<br />

clk<br />

1 clk_en ro[0]<br />

ri[0]<br />

tc_9_reg1<br />

un1_bank_end_tc_mod<br />

bank_end_tc_mod<br />

1<br />

row_end_gen_9<br />

reset row_end<br />

clk<br />

clk_en<br />

address[3:0]<br />

data_read_gen1_tc [3:0]<br />

bank_end_tc_out<br />

data_sel_pass1<br />

tc_bank_en_gen<br />

vec_rot_sel_pass2<br />

row_end_gen<br />

reset<br />

clk row_end<br />

1<br />

clk_en<br />

address[3:0]<br />

[3:0]<br />

read_address_gen1_msb<br />

row_end_gen<br />

1<br />

reset<br />

row_end<br />

clk<br />

clk_en<br />

address[3:0]<br />

read_address_gen1_lsb<br />

[3:0]<br />

bank_sel_cnt<br />

reg_genZ3<br />

reg_gen_enZ2<br />

1<br />

reset<br />

clk<br />

row_end<br />

clk_en<br />

address[3:0]<br />

reset<br />

clk<br />

ri[0]<br />

ro[0]<br />

reg_genZ3<br />

reset<br />

clk<br />

ro[0]<br />

ri[0]<br />

1<br />

reset<br />

clk<br />

clk_en<br />

ri[0]<br />

ro[0]<br />

bank_sel<br />

bank_sel_tc_gen1<br />

[3:0]<br />

input_data_read_sel<br />

bank_sel_gen1<br />

neg_edge_bank_sel<br />

row_end_10<br />

reg_genZ3<br />

reg_genZ3<br />

timing_cnt<br />

reg_genZ3<br />

reset<br />

reset<br />

cordic_clock<br />

load_en<br />

reset<br />

clk<br />

ro[0]<br />

ri[0]<br />

load_en_reg_rdwr<br />

global_reset_rdwr<br />

start<br />

reset<br />

output_en<br />

clk<br />

address[3:0]<br />

[3:0]<br />

rd_wr_gen1<br />

[3]<br />

rd_wr_x_sig<br />

reset<br />

clk<br />

ro[0]<br />

ri[0]<br />

reg_rdwr1<br />

clk<br />

ro[0]<br />

ri[0]<br />

reg_rdwr2<br />

rd_wr_x<br />

clk<br />

reg_genZ3<br />

reg_genZ3<br />

reset<br />

done_reset<br />

1<br />

done_counter<br />

reset<br />

clk<br />

clk_en<br />

tc<br />

reset<br />

clk<br />

ro[0]<br />

ri[0]<br />

reg_done1<br />

clk<br />

ro[0]<br />

ri[0]<br />

reg_done2<br />

done<br />

address[7:0]<br />

done_inst<br />

global_reset_out<br />

global_reset_out<br />

timing_cnt<br />

start<br />

reset<br />

output_en<br />

clk<br />

address[3:0]<br />

cordic_clk_by2_1<br />

[3:0]<br />

[2]<br />

cordic_clk_by2<br />

cordic_clk_by2<br />

Figure 8 shows the complex CORDIC block and the equivalent RTL is shown in Figure 9.<br />

Figure 8. Complex CORDIC<br />

clk<br />

xout_real_th[21:0]<br />

reset<br />

start<br />

output_en<br />

r_x_real_in[21:0]<br />

r_x_imag_in[21:0]<br />

Complex CORDIC<br />

xout_real_th_next[21:0]<br />

xout_imag_th[21:0]<br />

xin_real[21:0]<br />

xout_imag_th_next[21:0]<br />

xin_imag[21:0]<br />

vec_rot_sel<br />

80