Spectral Estimation Using a MUSIC Algorithm - Altera

Spectral Estimation Using a MUSIC Algorithm - Altera

Spectral Estimation Using a MUSIC Algorithm - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Spectral</strong> <strong>Estimation</strong> <strong>Using</strong> a <strong>MUSIC</strong> <strong>Algorithm</strong><br />

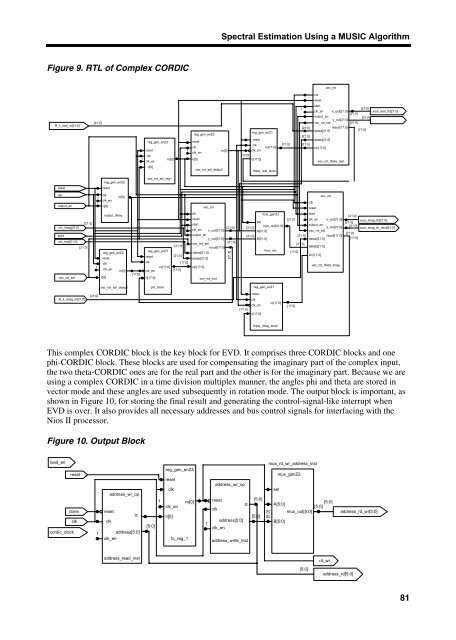

Figure 9. RTL of Complex CORDIC<br />

vec_rot<br />

clk<br />

reset<br />

R_x_real_in[21:0]<br />

[21:0]<br />

reg_gen_enZ2<br />

reset<br />

clk<br />

1 ro[0]<br />

clk_en<br />

1<br />

reg_gen_enZ2<br />

reset<br />

clk<br />

clk_en<br />

ri[0]<br />

ro[0]<br />

reg_gen_enZ1<br />

reset<br />

clk<br />

ro[17:0]<br />

clk_en<br />

[17:0]<br />

ri[17:0]<br />

[17:0]<br />

1<br />

[21:0]<br />

[21:0]<br />

[17:0]<br />

start<br />

[21:0]<br />

clk_en x_out[21:0]<br />

xout_real_th[21:0]<br />

[21:0]<br />

output_en<br />

[21:0]<br />

y_out[21:0]<br />

vec_rot_sel<br />

[21:0]<br />

result[17:0]<br />

dataa[21:0]<br />

[17:0]<br />

datab[21:0]<br />

zin[17:0]<br />

vec_rot_theta_real<br />

ri[0]<br />

vec_rot_sel_delay2<br />

theta_real_store<br />

reset<br />

reg_gen_enZ2<br />

reset<br />

vec_rot_sel_reg1<br />

clk<br />

output_en<br />

1<br />

clk<br />

clk_en<br />

ri[0]<br />

ro[0]<br />

vec_rot<br />

clk<br />

reset<br />

vec_rot<br />

output_delay<br />

[21:0]<br />

xin_imag[21:0]<br />

start<br />

xin_real[21:0]<br />

[21:0]<br />

reg_gen_enZ2<br />

reset<br />

clk<br />

1<br />

clk_en<br />

ro[0]<br />

vec_rot_sel<br />

ri[0]<br />

[17:0]<br />

1<br />

[21:0]<br />

reg_gen_enZ1<br />

reset<br />

[21:0]<br />

clk<br />

[17:0]<br />

ro[17:0]<br />

clk_en<br />

[17:0]<br />

ri[17:0]<br />

clk<br />

reset<br />

start<br />

[21:0]<br />

clk_en x_out[21:0]<br />

output_en<br />

y_out[21:0]<br />

vec_rot_sel<br />

[21:0]<br />

result[17:0]<br />

dataa[21:0]<br />

datab[21:0]<br />

zin[17:0]<br />

vec_rot_inst<br />

mux_genZ3<br />

sel<br />

mux_out[21:0]<br />

[21:0]<br />

A[21:0]<br />

[21:0]<br />

B[21:0]<br />

mux_vec<br />

start<br />

1 [21:0]<br />

[21:0] clk_en x_out[21:0]<br />

xout_imag_th[21:0]<br />

[21:0]<br />

output_en<br />

y_out[21:0]<br />

[21:0]<br />

xout_imag_th_next[21:0]<br />

vec_rot_sel<br />

[21:0]<br />

[21:0]<br />

result[17:0]<br />

dataa[21:0]<br />

[17:0]<br />

[21:0]<br />

datab[21:0]<br />

[17:0]<br />

zin[17:0]<br />

vec_rot_theta_imag<br />

vec_rot_sel_delay1<br />

phi_store<br />

reg_gen_enZ1<br />

R_x_imag_in[21:0]<br />

[21:0]<br />

[17:0]<br />

reset<br />

clk<br />

clk_en<br />

ri[17:0]<br />

ro[17:0]<br />

[17:0]<br />

theta_imag_store<br />

This complex CORDIC block is the key block for EVD. It comprises three CORDIC blocks and one<br />

phi-CORDIC block. These blocks are used for compensating the imaginary part of the complex input,<br />

the two theta-CORDIC ones are for the real part and the other is for the imaginary part. Because we are<br />

using a complex CORDIC in a time division multiplex manner, the angles phi and theta are stored in<br />

vector mode and these angles are used subsequently in rotation mode. The output block is important, as<br />

shown in Figure 10, for storing the final result and generating the control-signal-like interrupt when<br />

EVD is over. It also provides all necessary addresses and bus control signals for interfacing with the<br />

Nios II processor.<br />

Figure 10. Output Block<br />

load_en<br />

reset<br />

done<br />

clk<br />

cordic_clock<br />

1<br />

address_wr_op<br />

reset<br />

tc<br />

clk<br />

address[5:0]<br />

clk_en<br />

[5:0]<br />

1<br />

reg_gen_enZ4<br />

reset<br />

clk<br />

ro[0]<br />

clk_en<br />

ri[0]<br />

tc_reg_1<br />

address_wr_op<br />

reset<br />

[5:0]<br />

tc<br />

clk<br />

[5:0]<br />

address[5:0]<br />

1<br />

clk_en<br />

address_wirte_inst<br />

[5:0]<br />

mux_rd_wr_address_inst<br />

sel<br />

mux_genZ2<br />

[5:0]<br />

A[5:0]<br />

[5:0]<br />

mux_out[5:0]<br />

B[5:0]<br />

address_rd_wr[5:0]<br />

address_read_inst<br />

[5:0]<br />

rd_wr<br />

address_rd[5:0]<br />

81