F35-XXL Hardware description - Falcom

F35-XXL Hardware description - Falcom

F35-XXL Hardware description - Falcom

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>F35</strong>-<strong>XXL</strong> HARDWARE DESCRIPTION VERSION 1.10<br />

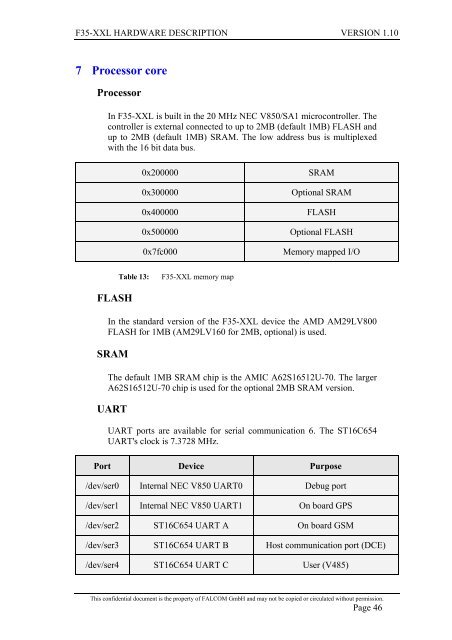

7 Processor core<br />

Processor<br />

In <strong>F35</strong>-<strong>XXL</strong> is built in the 20 MHz NEC V850/SA1 microcontroller. The<br />

controller is external connected to up to 2MB (default 1MB) FLASH and<br />

up to 2MB (default 1MB) SRAM. The low address bus is multiplexed<br />

with the 16 bit data bus.<br />

FLASH<br />

0x200000 SRAM<br />

0x300000 Optional SRAM<br />

0x400000 FLASH<br />

0x500000 Optional FLASH<br />

0x7fc000 Memory mapped I/O<br />

Table 13: <strong>F35</strong>-<strong>XXL</strong> memory map<br />

In the standard version of the <strong>F35</strong>-<strong>XXL</strong> device the AMD AM29LV800<br />

FLASH for 1MB (AM29LV160 for 2MB, optional) is used.<br />

SRAM<br />

The default 1MB SRAM chip is the AMIC A62S16512U-70. The larger<br />

A62S16512U-70 chip is used for the optional 2MB SRAM version.<br />

UART<br />

UART ports are available for serial communication 6. The ST16C654<br />

UART's clock is 7.3728 MHz.<br />

Port Device Purpose<br />

/dev/ser0 Internal NEC V850 UART0 Debug port<br />

/dev/ser1 Internal NEC V850 UART1 On board GPS<br />

/dev/ser2 ST16C654 UART A On board GSM<br />

/dev/ser3 ST16C654 UART B Host communication port (DCE)<br />

/dev/ser4 ST16C654 UART C User (V485)<br />

This confidential document is the property of FALCOM GmbH and may not be copied or circulated without permission.<br />

Page 46