Introduction to Quartus® II

Introduction to Quartus® II

Introduction to Quartus® II

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

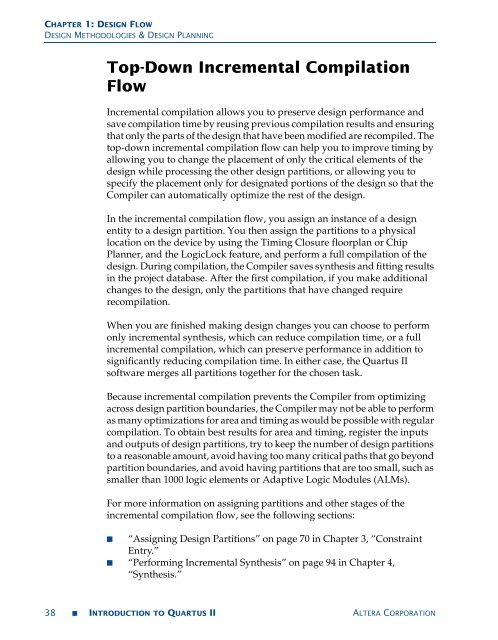

CHAPTER 1: DESIGN FLOW<br />

DESIGN METHODOLOGIES & DESIGN PLANNING<br />

Top-Down Incremental Compilation<br />

Flow<br />

Incremental compilation allows you <strong>to</strong> preserve design performance and<br />

save compilation time by reusing previous compilation results and ensuring<br />

that only the parts of the design that have been modified are recompiled. The<br />

<strong>to</strong>p-down incremental compilation flow can help you <strong>to</strong> improve timing by<br />

allowing you <strong>to</strong> change the placement of only the critical elements of the<br />

design while processing the other design partitions, or allowing you <strong>to</strong><br />

specify the placement only for designated portions of the design so that the<br />

Compiler can au<strong>to</strong>matically optimize the rest of the design.<br />

In the incremental compilation flow, you assign an instance of a design<br />

entity <strong>to</strong> a design partition. You then assign the partitions <strong>to</strong> a physical<br />

location on the device by using the Timing Closure floorplan or Chip<br />

Planner, and the LogicLock feature, and perform a full compilation of the<br />

design. During compilation, the Compiler saves synthesis and fitting results<br />

in the project database. After the first compilation, if you make additional<br />

changes <strong>to</strong> the design, only the partitions that have changed require<br />

recompilation.<br />

When you are finished making design changes you can choose <strong>to</strong> perform<br />

only incremental synthesis, which can reduce compilation time, or a full<br />

incremental compilation, which can preserve performance in addition <strong>to</strong><br />

significantly reducing compilation time. In either case, the Quartus <strong>II</strong><br />

software merges all partitions <strong>to</strong>gether for the chosen task.<br />

Because incremental compilation prevents the Compiler from optimizing<br />

across design partition boundaries, the Compiler may not be able <strong>to</strong> perform<br />

as many optimizations for area and timing as would be possible with regular<br />

compilation. To obtain best results for area and timing, register the inputs<br />

and outputs of design partitions, try <strong>to</strong> keep the number of design partitions<br />

<strong>to</strong> a reasonable amount, avoid having <strong>to</strong>o many critical paths that go beyond<br />

partition boundaries, and avoid having partitions that are <strong>to</strong>o small, such as<br />

smaller than 1000 logic elements or Adaptive Logic Modules (ALMs).<br />

For more information on assigning partitions and other stages of the<br />

incremental compilation flow, see the following sections:<br />

■ “Assigning Design Partitions” on page 70 in Chapter 3, “Constraint<br />

Entry.”<br />

■ “Performing Incremental Synthesis” on page 94 in Chapter 4,<br />

“Synthesis.”<br />

38 ■ INTRODUCTION TO QUARTUS <strong>II</strong> ALTERA CORPORATION