IntelR 80960 RN I/O Processor Datasheet

IntelR 80960 RN I/O Processor Datasheet

IntelR 80960 RN I/O Processor Datasheet

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

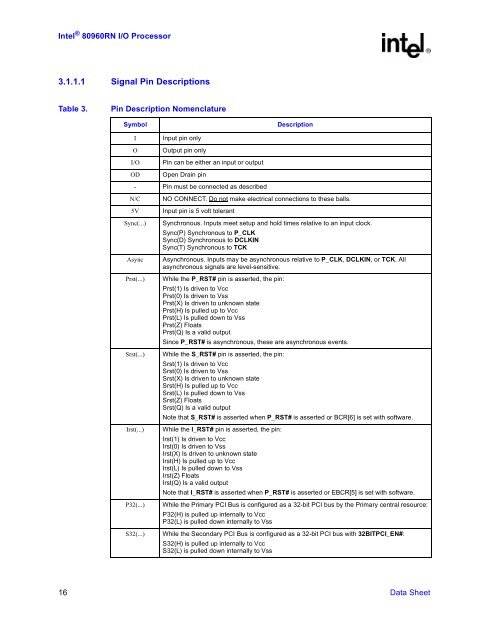

3.1.1.1 Signal Pin Descriptions<br />

Table 3.<br />

Pin Description Nomenclature<br />

Symbol<br />

Description<br />

I<br />

O<br />

I/O<br />

Input pin only<br />

Output pin only<br />

Pin can be either an input or output<br />

OD Open Drain pin<br />

- Pin must be connected as described<br />

N/C<br />

5V<br />

Sync(...)<br />

Async<br />

Prst(...)<br />

Srst(...)<br />

Irst(...)<br />

P32(...)<br />

S32(...)<br />

NO CONNECT. Do not make electrical connections to these balls.<br />

Input pin is 5 volt tolerant<br />

Synchronous. Inputs meet setup and hold times relative to an input clock.<br />

Sync(P) Synchronous to P_CLK<br />

Sync(D) Synchronous to DCLKIN<br />

Sync(T) Synchronous to TCK<br />

Asynchronous. Inputs may be asynchronous relative to P_CLK, DCLKIN, orTCK. All<br />

asynchronous signals are level-sensitive.<br />

While the P_RST# pin is asserted, the pin:<br />

Prst(1) Is driven to Vcc<br />

Prst(0) Is driven to Vss<br />

Prst(X) Is driven to unknown state<br />

Prst(H)IspulleduptoVcc<br />

Prst(L)IspulleddowntoVss<br />

Prst(Z) Floats<br />

Prst(Q) Is a valid output<br />

Since P_RST# is asynchronous, these are asynchronous events.<br />

While the S_RST# pin is asserted, the pin:<br />

Srst(1) Is driven to Vcc<br />

Srst(0) Is driven to Vss<br />

Srst(X) Is driven to unknown state<br />

Srst(H)IspulleduptoVcc<br />

Srst(L)IspulleddowntoVss<br />

Srst(Z) Floats<br />

Srst(Q) Is a valid output<br />

Note that S_RST# is asserted when P_RST# is asserted or BCR[6] is set with software.<br />

While the I_RST# pin is asserted, the pin:<br />

Irst(1) Is driven to Vcc<br />

Irst(0) Is driven to Vss<br />

Irst(X) Is driven to unknown state<br />

Irst(H)IspulleduptoVcc<br />

Irst(L)IspulleddowntoVss<br />

Irst(Z) Floats<br />

Irst(Q) Is a valid output<br />

Note that I_RST# is asserted when P_RST# is asserted or EBCR[5] is set with software.<br />

While the Primary PCI Bus is configured as a 32-bit PCI bus by the Primary central resource:<br />

P32(H) is pulled up internally to Vcc<br />

P32(L) is pulled down internally to Vss<br />

While the Secondary PCI Bus is configured as a 32-bit PCI bus with 32BITPCI_EN#:<br />

S32(H) is pulled up internally to Vcc<br />

S32(L) is pulled down internally to Vss<br />

16 Data Sheet