Product Specification

Product Specification

Product Specification

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Doc. version : 0.0<br />

Total pages : 24<br />

Date : 2007/01/23<br />

FOR PROMATE INTERNAL USE ONLY<br />

<strong>Product</strong> <strong>Specification</strong><br />

7.0" COLOR TFT-LCD MODULE<br />

MODEL NAME: A070VW04 V0<br />

< >Preliminary <strong>Specification</strong><br />

< >Final <strong>Specification</strong><br />

Note: The content of this<br />

specification is subject to change.<br />

© 2006 AU Optronics<br />

All Rights Reserved,<br />

Do Not Copy.

Version: 0.0<br />

Page: 1/24<br />

Record of Revision<br />

Version Revise Date Page Content<br />

0 2007/01/23 Draft.<br />

FOR PROMATE INTERNAL USE ONLY<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 2/24<br />

Contents<br />

A. General Description ........................................................................................................ 3<br />

B. Features ........................................................................................................................... 3<br />

C. General Information ........................................................................................................ 4<br />

D. Outline Dimension........................................................................................................... 5<br />

1. TFT-LCD Module – Front View ...................................................................................................................5<br />

2. TFT-LCD Module – Rear View.....................................................................................................................6<br />

E. Electrical <strong>Specification</strong>s ................................................................................................. 7<br />

1. FPC Pin Assignment (HRS FH27-60S-0.4SH).........................................................................................7<br />

2 Absolute Maximum Ratings ........................................................................................................................9<br />

F. Electrical Characteristics.............................................................................................. 10<br />

1 TFT- LCD Typical Operation Condition (AGND = AGND2 = GND = GGND = 0V)..................................10<br />

2. Backlight Driving Conditions ...................................................................................................................10<br />

3. AC Characteristics ....................................................................................................................................11<br />

4. RGB Parallel Input Timing ........................................................................................................................11<br />

5. Serial Control Interface AC Characteristic..............................................................................................13<br />

6. Register Information .................................................................................................................................14<br />

7. Register Table ............................................................................................................................................15<br />

8. Register Description .................................................................................................................................15<br />

9. Suggested Application Circuit .................................................................................................................19<br />

G. Optical specification ..................................................................................................... 21<br />

FOR PROMATE INTERNAL USE ONLY<br />

H. Absolute Ratings of Ambient Environment ................................................................ 23<br />

I. Packing Form................................................................................................................. 24<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 3/24<br />

A. General Description<br />

A070VW04 is a amorphous transmissive type TFT (Thin Film Transistor) LCD (Liquid crystal Display). This<br />

model is composed of TFT-LCD, drive IC, FPC (flexible printed circuit), and backlight unit.The timing<br />

controller is embedded, so it is easily to design for consumer product.<br />

B. Features<br />

7-inch display size<br />

WVGA resolution and stripe dot arrangement<br />

Built in timing controller<br />

LED backlight<br />

Standby mode supported<br />

<br />

<br />

<br />

<br />

<br />

<br />

Up/Down, Left/Right reversion selection<br />

SYNC + DE Mode<br />

Parallel 18/24bits interface support<br />

16 M color supported<br />

Wide viewing angle<br />

RoHS compliant green design<br />

FOR PROMATE INTERNAL USE ONLY<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 4/24<br />

C. General Information<br />

NO. Item Unit <strong>Specification</strong> Remark<br />

1 Display Resolution dot 800RGB(H)×480(V)<br />

2 Active Area mm 152.40(H)×91.44(V)<br />

3 Screen Size inch 7.0(Diagonal)<br />

4 Pixel Pitch mm 0.1905(H)×0.1905(V)<br />

5 Color Configuration -- R. G. B. Stripe Note 1<br />

6 Color Depth -- 16.7M Colors Note 2<br />

7 Overall Dimension mm 164(H) × 103(V) × 5.1(T) Note 3<br />

8 Weight g 153.5 +/- 10%<br />

9 Panel surface treatment -- Anti-Glare<br />

10 Display Mode -- Normally White<br />

Note 1: Below figure shows dot stripe arrangement.<br />

…………………………<br />

…….<br />

FOR PROMATE INTERNAL USE ONLY<br />

…<br />

…<br />

…………………………<br />

…….<br />

(1……………………..480)<br />

…………<br />

…<br />

( 1 2 3…………………………….2398 2399 2400)<br />

Note 2: The full color display depends on 8-bit data signal (pin 4~27).<br />

Note 3: Not include blacklight cable and FPC. Refer next page to get further information.<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 5/24<br />

D. Outline Dimension<br />

1. TFT-LCD Module – Front View<br />

FOR PROMATE INTERNAL USE ONLY<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED, OR TRANSFORMED TO ANY OTHER FORMS<br />

WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 6/24<br />

2. TFT-LCD Module – Rear View<br />

FOR PROMATE INTERNAL USE ONLY<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED, OR TRANSFORMED TO ANY OTHER FORMS<br />

WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 7/24<br />

E. Electrical <strong>Specification</strong>s<br />

1. FPC Pin Assignment (HRS FH27-60S-0.4SH)<br />

Pin no Symbol I/O Description<br />

1 AGND2 P Analog Ground<br />

2 AVDD2 P Analog Power<br />

3 VDD P Digital Power<br />

4 R0 I Data input (LSB)<br />

5 R1 I Data input<br />

6 R2 I Data input<br />

7 R3 I Data input<br />

8 R4 I Data input<br />

9 R5 I Data input<br />

10 R6 I Data input<br />

11 R7 I Data input (MSB)<br />

12 G0 I Data input (LSB)<br />

13 G1 I Data input<br />

14 G2 I Data input<br />

15 G3 I Data input<br />

16 G4 I Data input<br />

17 G5 I Data input<br />

18 G6 I Data input<br />

FOR PROMATE INTERNAL USE ONLY<br />

19 G7 I Data input (MSB)<br />

20 B0 I Data input (LSB)<br />

21 B1 I Data input<br />

22 B2 I Data input<br />

23 B3 I Data input<br />

24 B4 I Data input<br />

25 B5 I Data input<br />

26 B6 I Data input<br />

27 B7 I Data input (MSB)<br />

28 DCLK I Clock input<br />

29 DE I Data enable signal<br />

30 HSYNC I Horizontal sync input. Negative polarity<br />

31 VSYNC I Vertical sync input. Negative polarity<br />

32 SCL I Serial communication clock input<br />

33 SDA I Serial communication data input<br />

34 CSB I Serial communication chip select<br />

35 FBA I DCDC feed back signal<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 8/24<br />

36 VDD P Digital Power<br />

37 DRVA O DCDC PWM signal<br />

38 GND P Digital ground<br />

39 AGND1 P Analog ground<br />

40 AVDD1 P Analog Power<br />

41 VCOMin I For external VCOM DC input (Optional)<br />

42 NC - Not connect<br />

43 NC - Not connect<br />

44 VCOM O connect a capacitor<br />

45 V10 P Gamma correction voltage reference<br />

46 V9 P Gamma correction voltage reference<br />

47 V8 P Gamma correction voltage reference<br />

48 V7 P Gamma correction voltage reference<br />

49 V6 P Gamma correction voltage reference<br />

50 V5 P Gamma correction voltage reference<br />

51 V4 P Gamma correction voltage reference<br />

52 V3 P Gamma correction voltage reference<br />

53 V2 P Gamma correction voltage reference<br />

54 V1 P Gamma correction voltage reference<br />

55 NC - Not connect<br />

56 VGH P Positive power for TFT<br />

57 GVCC P Digital Power<br />

58 VGL P Negative power for TFT<br />

59 GGND P Digital Ground<br />

60 CAP C Connected to a capacitor<br />

I: Input pin; P: Power pin; G: Ground pin; C: capacitor pin<br />

FOR PROMATE INTERNAL USE ONLY<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 9/24<br />

2 Absolute Maximum Ratings<br />

Item Symbol Condition Min. Max. Unit Remark<br />

VCC GND=0 -0.5 5 V Note 1<br />

Power voltage<br />

AVDD AGND=0 -0.5 15 V Note 1<br />

Operating<br />

Ambient<br />

Topa -- 0 60 <br />

temperature<br />

Temperature<br />

Storage<br />

Ambient<br />

Tstg -- -10 70 <br />

temperature<br />

Temperature<br />

Note 1: Functional operation should be restricted under normal ambient temperature.<br />

FOR PROMATE INTERNAL USE ONLY<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 10/24<br />

F. Electrical Characteristics<br />

The following items are measured under stable condition and suggested application circuit.<br />

1 TFT- LCD Typical Operation Condition (AGND = AGND2 = GND = GGND = 0V)<br />

ITEM Symbol MIN. TYP. MAX. UNIT Remark<br />

VCC 3.3 3.6 V<br />

Power supply<br />

AVDD TBD TBD TBD V<br />

VGH TBD TBD TBD V<br />

VGL TBD TBD TBD V<br />

Input<br />

H Level V IH 0.7V CC - V CC V<br />

Signal L Level V IL GND - 0.3V CC V<br />

Input Reference V1 ~ V5 AVDD/2 - AVDD – 0.1 V<br />

Voltage V6 ~ V10 0.1 - AVDD/2 V<br />

VCOM V CDC TBD TBD TBD V<br />

Note: Above every operation range is based on stable operation from suggested application circuit.<br />

2. Backlight Driving Conditions<br />

Parameter Symbol Min. Typ. Max. Unit Remark<br />

LED lightbar Current I L --- 160 --- mA ---<br />

LED light bar Voltage V L --- 12 --- V ---<br />

LED Life Time L L 10,000 --- --- Hr Note 2, 3<br />

Note 1: The LED driving condition is defined for LED module (21 LED).<br />

FOR PROMATE INTERNAL USE ONLY<br />

Note 2: Define “LED Lifetime”: brightness is decreased to 50% of the initial value. LED Lifetime is<br />

restricted under normal condition, ambient temperature = 25 and LED lightbar voltage = 12V.<br />

Note 3: If it uses larger LED lightbar voltage more than 12V, it maybe decreases the LED lifetime.<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 11/24<br />

3. AC Characteristics<br />

PARAMETER SYMBOL CONDITIONS MIN. TYP. MAX. UNIT<br />

Clock High time T WCL 8 - - ns<br />

Clock Low time T WCH 8 - - ns<br />

Clock rising time T RCLK - - 1 ns<br />

Clock falling time T ACK - - 1 ns<br />

Hsync setup time T HSU 5 ns<br />

Vs<br />

Hs<br />

VIH<br />

VIL<br />

VIH<br />

VIL<br />

Hsync hold time T HHD 10 ns<br />

Vsync setup time T VSU 0 ns<br />

Vsync hold time T VHD 2 ns<br />

Data setup time T DSU 5 ns<br />

Data hold time T DHD 10 ns<br />

Data enable set-up time T ESU 4 ns<br />

Data enable hold time T EHD 2 ns<br />

T VPD<br />

RGB,<br />

DE, Hs<br />

CLK<br />

FOR PROMATE INTERNAL USE ONLY<br />

Figure 1 : Input timing details<br />

VIH<br />

VIL<br />

VIH<br />

VIL<br />

T DS,<br />

T ES,<br />

T HS<br />

T DH,<br />

T HE,<br />

T HH<br />

T CH<br />

T CL<br />

4. RGB Parallel Input Timing<br />

a. Horizontal Timing<br />

PARAMETER SYMBOL CONDITIONS MIN. TYP. MAX UNIT<br />

DCLK frequency F DCLK 25 33 40 MHz<br />

DCLK period T DCLK 25 30.3 40 ns<br />

Hsync Period (= T HD + T HBL ) T H 986 1056 1183 DCLK<br />

Active Area T HD - 800 - DCLK<br />

Horizontal blanking (= T HF + T HE ) T HBL 186 256 383 CLK<br />

Hsync front porch T HF 40 - CLK<br />

Delay from Hsync to 1 st data input<br />

(= T HW + T HB )<br />

T HE<br />

Function of<br />

HDL[5..0] settings<br />

146 216 343 DCLK<br />

Hsync pulse width T HW 1 128 136 CLK<br />

Hsync back porch T HB 10 88 342 CLK<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 12/24<br />

b. Vertical Timing<br />

PARAMETER SYMBOL CONDITIONS MIN. TYP. MAX. UNIT<br />

HS<br />

DCLK<br />

R[7:0]<br />

G[7:0]<br />

B[7:0]<br />

Vsync period (= T VD + T VBL ) T V 497 505 512 Th<br />

Active lines T VD 480 Th<br />

Vertical blanking (= T VF + T VE ) T VBL 17 25 32 Th<br />

Vsync front porch T VF 1 - Th<br />

GD start pulse delay<br />

T VE<br />

Function of<br />

VDL[3..0] settings<br />

16 24 31 HS<br />

Vsync pulse width T VW 1 3 16 Th<br />

Hsync/ Vsync phase shift T VPD 2 320 - CLK<br />

THF<br />

Rn-1 Rn<br />

Gn-1 Gn<br />

THW<br />

Invalid<br />

Invalid<br />

Bn-1 Bn<br />

Invalid<br />

THE<br />

THB<br />

TH<br />

R0 R1 R2 R3<br />

Rn-1 Rn Invalid<br />

G0 G1 G2 G3<br />

Gn-1 Gn Invalid<br />

B0 B1 B2 B3<br />

Bn-1 Bn Invalid<br />

THBL<br />

THD<br />

FOR PROMATE INTERNAL USE ONLY<br />

Figure 2 Horizontal input timing. (HV mode)<br />

THBL<br />

THD<br />

DE<br />

DCLK<br />

R[7:0]<br />

Rn-1<br />

Rn<br />

Invalid<br />

R0<br />

R1<br />

R2<br />

R3<br />

Rn-1<br />

Rn<br />

Invalid<br />

G[7:0]<br />

Gn-1<br />

Gn<br />

Invalid<br />

G0<br />

G1<br />

G2<br />

G3<br />

Gn-1<br />

Gn<br />

Invalid<br />

B[7:0]<br />

Bn-1<br />

Bn<br />

Invalid<br />

B0<br />

B1<br />

B2<br />

B3<br />

Bn-1<br />

Bn<br />

Invalid<br />

Figure 3: Horizontal input timing. (DE mode)<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 13/24<br />

T V<br />

Vs<br />

T VF<br />

T VW<br />

Hs<br />

T VE<br />

Line<br />

T VF<br />

T H<br />

Xn-1 Xn X1 X2 X3 Xn-1 Xn<br />

Invalid<br />

T VBL<br />

T VD<br />

Figure 4: Vertical timing. (HV mode)<br />

DE<br />

Line Xn-1 Xn X1 X2 X3 Xn-1 Xn<br />

Invalid<br />

T VBL<br />

TVD<br />

Figure 5: Vertical timing. (DE mode)<br />

5. Serial Control Interface AC Characteristic<br />

PARAMETER SYMBOL CONDITIONS MIN. TYP. MAX. UNIT<br />

Serial clock T SCK 320 ns<br />

SCL pulse duty T SCW 40 50 60 %<br />

Serial data setup time T IST 120 ns<br />

Serial data hold time T IHD 120 ns<br />

Serial clock high/low T SSW 120 ns<br />

CSB setup time T CST 120 ns<br />

CSB hold time T CHD 120 ns<br />

Chip select distinguish T CD 1 us<br />

Delay from CSB to VSYNC T CV 1 us<br />

Serial data output delay T ID CL=20pF - - 60 ns<br />

FOR PROMATE INTERNAL USE ONLY<br />

Vsync<br />

30%<br />

T CV<br />

CSB<br />

30%<br />

30%<br />

SDA<br />

SCL<br />

T CST<br />

T CHD<br />

T CD<br />

70%<br />

D15 D14 D13 D2 D1 D0<br />

30%<br />

T IST<br />

T IHD<br />

T SSW<br />

T SSW<br />

D15 D14 D13 D12<br />

70%<br />

30%<br />

Figure 6 : AC serial interface write mode timing<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 14/24<br />

CSB<br />

30%<br />

30%<br />

T CST<br />

T CHD<br />

T CD<br />

SDA<br />

70%<br />

30%<br />

D15 D14 D13<br />

D12 D11 D10 D9 D8 D7 D1<br />

D0<br />

T IST<br />

T IHD<br />

T SSW T SSW<br />

T ID<br />

SCL<br />

70%<br />

30%<br />

T SCK<br />

6. Register Information<br />

Figure 7 : AC serial interface read mode timing<br />

There is a total of 6 registers each containing several parameters. For a detailed description of the<br />

parameters refer to register table.The serial register has read/write function. D[15:12] are the register<br />

address, D[11] defines the read or write mode and D[10:0] are the data.<br />

Figure 8: Serial interface write/read sequence<br />

FOR PROMATE INTERNAL USE ONLY<br />

1. At power-on, the default values specified for each parameter are taken.<br />

2. If less than 16-bit data are read during the CS low time period, the data is cancelled.<br />

a. The write operation is cancelled.<br />

b. The read operation is interrupt.<br />

3. If more than 16-bit data are read during the CS low time period, the last 16 bits are kept.<br />

a. Address & R/W are always defined form CSB falling edge.<br />

b. The write operation load last 11 bit data before CSB rising edge.<br />

c. The read operation is “D0” is output to SDA until CSB rising edge.<br />

4. All items are set at the falling edge of the vertical sync, except R0[1:0].<br />

5. When GRB is activated through the serial interface, all registers are cleared, except the GRB value.<br />

6. Register R/W setting: D11 = “L” write mode; D11 = “H” read mode.<br />

7. The register setting values are valid when VCC already goes to high and after VSYNC starts.<br />

8. It is suggested that VSYNC, HSYNC, DCLK always exists in the same time. But if HSYNC, DCLK stops,<br />

only VSYNC operating, the register setting is still valid.<br />

9. If the chip goes to standby mode, the register value will still keep. MCU can wake up the chip only by<br />

changing standby mode value from low to high.<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 15/24<br />

10. The register setting values are rewritten by the influence of static electricity, a noise, etc. to unsuitable<br />

value, incorrect operating may occur. It is suggested that the SPI interface will setup as frequently as<br />

possible.<br />

7. Register Table<br />

Reg<br />

ADDRESS R/W DATA<br />

No. D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0<br />

R0 0 0 0 0 R/W 01 01<br />

R1 0 0 0 1 R/W X 01<br />

DITH<br />

(1)<br />

VCOM_M<br />

(10)<br />

R2 0 0 1 0 R/W X X X HDL<br />

R3 0 0 1 1 R/W X X X X<br />

R6 0 1 1 0 R/W X 0<br />

EnGB12 EnGB11 EnGB10<br />

(0) (1) (0)<br />

U/D<br />

(0)<br />

SHL<br />

(1)<br />

0 0<br />

SHDB1<br />

(1)<br />

0<br />

VCOM_LVL<br />

(2Fh)<br />

EnGB5<br />

(0)<br />

EnGB4<br />

(1)<br />

GRB<br />

(1)<br />

EnGB3<br />

(0)<br />

R15 1 1 1 1 R/W X X X X X X X X X 1 1<br />

X : Reserved, please set to “0”.<br />

8. Register Description<br />

R0 settings<br />

Address Bit Description Default<br />

0000 [10..0] Bits 10-9 AUO Internal Use 01<br />

Bits7-8 AUO Internal Use 01<br />

Bit6 (DITH)<br />

Bit5 (U/D)<br />

Dithering function.<br />

FOR PROMATE INTERNAL USE ONLY<br />

Vertical shift direction selection.<br />

Bit4 (SHL) Horizontal shift direction selection.<br />

Bit3 (SHDB1)<br />

AVDD DC-DC converter shutdown setting.<br />

Bit2 AUO Internal Use 0<br />

Bit1 (GRB)<br />

Bit0 (STB)<br />

Global reset.<br />

Standby mode setting.<br />

STB<br />

(1)<br />

0<br />

Bit6 DITH function<br />

0 DITH off.<br />

1 DITH on. (default)<br />

Bit5 U/D function<br />

0 Scan down; First line=Gn Gn-1 … G2 Last line=G1. (default)<br />

1 Scan up; First line=G1 G2 … Gn-1 Last line=Gn.<br />

Bit4<br />

SHL function<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 16/24<br />

0 Shift left; First data=Y600 Y601 … Y2 Last data=Y1.<br />

1 Shift right: First data=Y1 Y2 … Y600 Last data=Y600. (default)<br />

Bit3 SHDB1 function<br />

0 AVDD DC-DC converter is off.<br />

1 AVDD DC-DC converter is on. (default)<br />

Bit1<br />

GRB function<br />

0 The controller is reset. Reset all registers to default value.<br />

1 Normal operation. (default)<br />

Bit0<br />

STB function<br />

0 T-CON, source driver and DC-DC converters are off, and all outputs are High-Z.<br />

1 Normal operation. (default)<br />

R1 settings<br />

Address Bit Description Default<br />

0001 [8..0] Bit9-8 AUO Internal Use 01<br />

Bit7-6<br />

Bit7-6<br />

(VCOM_M)<br />

Bit5-0<br />

(VCOM_LVL)<br />

VCOM_M function.<br />

VCOM mode signal.<br />

VCOM level adjustment.<br />

Step 31.25mV/LSB @AVDD=12.5V<br />

(AVDD/400)<br />

00 VCOM generator disabled. VCOM is generated externally.<br />

01 VCOM internal reference disabled. DC voltage of VCOM follows VCOMin signal.<br />

1x<br />

FOR PROMATE INTERNAL USE ONLY<br />

VCOM generator enabled. DC voltage of VCOM follows VCOM_LVL settings. (default)<br />

NOTE: Please refer to to Figure40.<br />

Bit5-0 VCOM_LVL function @V1=12.5V<br />

00h VCOM_LVL = V1/2–47*31.25mV = 4.78125V<br />

01h VCOM_LVL = V1/2–46*31.25mV = 4.8125V<br />

2Fh VCOM_LVL = V1/2 = 6.25V (default)<br />

3Eh VCOM_LVL = V1/2+15*31.25mV = 6.71875V<br />

3Fh VCOM_LVL = V1/2+16*31.25mV = 6.75V<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 17/24<br />

R2 settings<br />

Address Bit Description Default<br />

0010 [7..0] Bit7-0 (HDL) Horizontal start pulse adjustment function<br />

Bit7-0<br />

00h<br />

80h<br />

FFh<br />

HDL function.<br />

T HE = T HEtyp – 128 CLK period.<br />

T HE = T HEtyp . (default)<br />

T HE = T HEtyp + 127 CLK period.<br />

R3 settings<br />

Address Bit Description Default<br />

0011 6..0] Bit6 AUO Internal Use 0<br />

Bit5 AUO Internal Use 0<br />

Bit4 AUO Internal Use 0<br />

Bit3-0 (VDL) Vertical start pulse adjustment function<br />

Bit3-0 VDL function.<br />

0000 T VE = T VEtyp – 8 Hs period.<br />

0001 T VE = T VEtyp – 7 Hs period.<br />

0010 T VE = T VEtyp – 6 Hs period.<br />

0011 T VE = T VEtyp – 5 Hs period.<br />

FOR PROMATE INTERNAL USE ONLY<br />

0100 T VE = T VEtyp – 4 Hs period.<br />

0101 T VE = T VEtyp – 3 Hs period.<br />

0110 T VE = T VEtyp – 2 Hs period.<br />

0111 T VE = T VEtyp – 1 Hs period.<br />

1000 T VE = T VEtyp . (default)<br />

1001 T VE = T VEtyp + 1 Hs period.<br />

1010 T VE = T VEtyp + 2 Hs period.<br />

1011 T VE = T VEtyp + 3 Hs period.<br />

1100 T VE = T VEtyp + 4 Hs period.<br />

1101 T VE = T VEtyp + 5 Hs period.<br />

1110 T VE = T VEtyp + 6 Hs period.<br />

1111 T VE = T VEtyp + 7 Hs period.<br />

R6 settings<br />

Address Bit Description Default<br />

0110 [9..0] Bit9 AUO Internal Use 0<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 18/24<br />

Bit8(EnGB12) Gamma buffer Enable for V12<br />

Bit7(EnGB11) Gamma buffer Enable for V11<br />

Bit6(EnGB10) Gamma buffer Enable for V10<br />

Bit5 AUO Internal Use 0<br />

Bit4 AUO Internal Use 0<br />

Bit3(EnGB5) Gamma buffer Enable for V5<br />

Bit2(EnGB4) Gamma buffer Enable for V4<br />

Bit1(EnGB3) Gamma buffer Enable for V3<br />

Bit0 AUO Internal Use 0<br />

Bitx EnGBx function<br />

0 Gamma buffer for VX is disable (High Z).<br />

1 Gamma buffer is enable. VX must be connected externally.<br />

FOR PROMATE INTERNAL USE ONLY<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 19/24<br />

9. Suggested Application Circuit<br />

0.1uF/10V/X5R/0402<br />

0.1uF/25V/X5R/0603<br />

C417<br />

C421<br />

1uF/35V/X5R/0603<br />

C414<br />

R412<br />

3.3V<br />

0/5%/0603<br />

CXLP100-100(10uH)<br />

L402<br />

R414<br />

CXLP100<br />

6.8K/5%/0603<br />

5V<br />

2<br />

1<br />

DM405<br />

K<br />

A<br />

DAN217U<br />

C415<br />

0.1uF/25V/X5R/0603<br />

+10V<br />

10uF/10V/X5R/0805<br />

C418<br />

10nF/50V/X5R/0603<br />

16<br />

D404<br />

R432<br />

15<br />

1 3<br />

AVDD2<br />

14<br />

SB07-03C<br />

13<br />

C430<br />

R433<br />

12<br />

22uF/16V/X5R/1206 0/5%/0603<br />

11<br />

261/5%/0603<br />

10<br />

R430<br />

9<br />

EN<br />

R427 R428<br />

C429<br />

0/5%/0603<br />

2.2uF/25V/X5R/0805<br />

110K/1%/0603 0/5%/0603<br />

DAN217U<br />

C428<br />

27pF/50V/X5R/0603<br />

1<br />

C424<br />

A<br />

3<br />

R429<br />

R425 R424<br />

C<br />

0.1uF/25V/X5R/0603<br />

2<br />

70K/1%/0603<br />

K<br />

10/1%/0603<br />

0/5%/0603<br />

DM407<br />

R426<br />

10K/1%/0603<br />

C<br />

3<br />

C413<br />

0.1uF/25V/X5R/0603<br />

2<br />

22nF/50V/X5R/0603<br />

C420<br />

NO(0/5%/0603)<br />

R415<br />

1<br />

FB_1 2<br />

3<br />

4<br />

5<br />

6<br />

FB_2 7<br />

FB_3 8<br />

R417<br />

10K/1%/0603<br />

R418<br />

10K/1%/0603<br />

U401<br />

/RDY<br />

CT<br />

FB1<br />

SW<br />

COMP PGND<br />

IN<br />

IN3<br />

GND<br />

GH<br />

REF<br />

IN2<br />

FB2<br />

GL<br />

FB3<br />

EN<br />

MP1530<br />

3.3V<br />

C416<br />

2.2uF/35V/X5R/0805<br />

2<br />

DM406<br />

VGH2<br />

R431<br />

5.1K/5%/0603<br />

+15V<br />

VGL2<br />

R422<br />

DAN217U<br />

0/5%/0603<br />

NO(RB551V-30)<br />

C422<br />

R420 R419<br />

1<br />

2.2uF/35V/X5R/0805<br />

C425<br />

A<br />

D405<br />

3<br />

56K/1%/0603 0/5%/0603<br />

C<br />

C423<br />

0.1uF/25V/X5R/0603<br />

2<br />

27pF/50V/X5R/0402<br />

K<br />

DM408<br />

C427<br />

2.2uF/35V/X5R/0805<br />

2<br />

R423<br />

1<br />

0/5%/0603<br />

FOR PROMATE INTERNAL USE ONLY<br />

R416<br />

1<br />

K<br />

A<br />

C<br />

DAN217U<br />

3<br />

-7V<br />

5.1k/1%/0603<br />

1uF/35V/X5R/0603<br />

C426<br />

C419<br />

100K/5%/0603<br />

R413<br />

R421<br />

10/1%/0603<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED, OR TRANSFORMED TO ANY OTHER FORMS<br />

WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 20/24<br />

J501<br />

VCOM<br />

R301 R302<br />

AVDD<br />

R306<br />

0/5%/0603<br />

V1<br />

V2<br />

V3<br />

V4<br />

V5<br />

R316<br />

0/5%/0603<br />

R320<br />

0/5%/0603<br />

R321<br />

V6<br />

FBA<br />

3.3V<br />

DRVA<br />

DGND<br />

R508<br />

AVDD<br />

VCOMin<br />

10/5%/0603<br />

VCOM<br />

V10<br />

V9<br />

V8<br />

V7<br />

V6<br />

V5<br />

V4<br />

V3<br />

V2<br />

V1<br />

1<br />

2<br />

AGND2<br />

3<br />

AVDD2<br />

R0 4<br />

VDD<br />

R1 5<br />

R0<br />

R2 6<br />

R1<br />

R3 7<br />

R2<br />

R4 8<br />

R3<br />

R5 9<br />

R4<br />

R6 10<br />

R5<br />

R7 11<br />

R6<br />

G0 12<br />

R7<br />

G1 13<br />

G0<br />

G2 14<br />

G1<br />

G3 15<br />

G2<br />

G4 16<br />

G3<br />

G5 17<br />

G4<br />

G6 18<br />

G5<br />

G7 19<br />

G6<br />

B0 20<br />

G7<br />

B1 21<br />

B0<br />

B2 22<br />

B1<br />

B3 23<br />

B2<br />

B4 24<br />

B3<br />

B5 25<br />

B4<br />

B6 26<br />

B5<br />

B7 27<br />

B6<br />

DCLK 28<br />

B7<br />

DE 29<br />

DCLK<br />

HS 30<br />

DE<br />

VS 31<br />

HSYNC<br />

SCL 32<br />

VSYNC<br />

SDA 33<br />

SCL<br />

CSB 34<br />

SDA<br />

35<br />

CSB<br />

36<br />

FBA<br />

37<br />

VDD<br />

38<br />

DRVA<br />

39<br />

GND<br />

40<br />

AGND1<br />

41<br />

AVDD1<br />

42<br />

VCOMin<br />

43<br />

NC<br />

44<br />

NC<br />

45<br />

VCOM<br />

46<br />

V10<br />

47<br />

V9<br />

48<br />

V8<br />

49<br />

V7<br />

50<br />

V6<br />

51<br />

V5<br />

52<br />

V4<br />

53<br />

V3<br />

54<br />

V2<br />

55<br />

V1<br />

56<br />

NC<br />

57<br />

VGH<br />

58<br />

VGL<br />

59<br />

GVCC<br />

60<br />

GGND<br />

CAP<br />

CON60<br />

C505<br />

DGND<br />

1uF/16V/X5R/0603<br />

C306<br />

1uF/16V/X5R/0603<br />

C309<br />

R311<br />

2.4K/1%/0603<br />

R313<br />

850/1%/0603<br />

R314<br />

0/5%/0603<br />

R315<br />

400/1%/0603<br />

AVDD<br />

3.3V<br />

C506<br />

1uF/16V/X5R/0603<br />

C305<br />

C304<br />

C303<br />

1uF/16V/X5R/0603<br />

500/1%/0603 0/5%/0603 R303<br />

C308<br />

10uF/10V/X5R/K/0805<br />

R312<br />

R319<br />

1.53K/1%/0603<br />

500/1%/0603<br />

0/5%/0603<br />

0/5%/0603<br />

V8<br />

V9<br />

VGH<br />

VGL<br />

DGND<br />

AVDD<br />

AVDD<br />

VR301<br />

EVM3RSX50B14<br />

R515<br />

U301A<br />

R324<br />

0/5%/0603<br />

R325<br />

0/5%/0603<br />

R516<br />

VCOM<br />

NO(10K/5%/0603)<br />

C324<br />

10uF/10V/X5R/K/0805<br />

1uF/16V/X5R/0603<br />

C310<br />

1uF/16V/X5R/0603<br />

1.54K/1%/0603<br />

R304<br />

0/5%/0603<br />

R308<br />

0/5%/0603<br />

V7<br />

1uF/16V/X5R/0603<br />

C322<br />

1uF/16V/X5R/0603<br />

C311<br />

10uF/16V/X5R/1206<br />

C301<br />

0.1uF/16V/X5R/0402<br />

C302<br />

R307<br />

400/1%/0603<br />

R309<br />

840/1%/0603<br />

R310<br />

R317<br />

520/1%/0603<br />

R318<br />

0/5%/0603<br />

C323<br />

0.1uF/16V/X5R/K/0402<br />

10uF/10V/X5R/K/0805<br />

0/5%/0603<br />

V10<br />

3<br />

4<br />

1<br />

NO(AD8565)<br />

0/5%/0603<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED, OR TRANSFORMED TO ANY OTHER FORMS<br />

WITHOUT PERMISSION FROM AU OPTRONICS CORP.<br />

+<br />

-<br />

FOR PROMATE INTERNAL USE ONLY<br />

5<br />

2<br />

1uF/16V/X5R/0603<br />

C307<br />

1uF/16V/X5R/0603<br />

R305<br />

520/1%/0603<br />

R322<br />

3.3V<br />

R323<br />

0/5%/0603<br />

VCOMin

Signal(Relative value)<br />

Version: 0.0<br />

Page: 21/24<br />

G. Optical specification<br />

Item Symbol Condition Min. Typ. Max. Unit Remark<br />

Response Time<br />

Rise<br />

Fall<br />

Contrast ratio<br />

Viewing Angle<br />

Top<br />

Bottom<br />

Left<br />

Right<br />

Tr<br />

- 12 20 ms Note 3<br />

θ=0°<br />

Tf<br />

- 18 30 ms<br />

CR<br />

At optimized<br />

viewing angle<br />

200 400 - Note 4<br />

30 40 -<br />

CR10<br />

50<br />

50<br />

60<br />

60<br />

50 60 -<br />

- deg. Note 5<br />

-<br />

Brightness Y L θ=0° 150 200 - cd/m 2 Note 6<br />

White Chromaticity<br />

X θ=0° 0.25 0.30 0.35<br />

y θ=0° 0.27 0.32 0.37<br />

Note 1:Ambient temperature =25 ℃ , and LED<br />

lightbar voltage V L = 12 V. To be measured<br />

---------------------------<br />

in the dark room.<br />

----<br />

Note 2:To be measured on the center area of panel<br />

with a viewing cone of 1° by Topcon<br />

luminance meter BM-7, after 15 minutes<br />

operation.<br />

FOR PROMATE INTERNAL USE ONLY<br />

Note 3. Definition of response time:<br />

The output signals of photo detector are measured when the input signals are changed from “black” to<br />

“white”(falling time) and from “white” to “black”(rising time), respectively.<br />

The response time is defined as the time interval between the 10% and 90% of amplitudes. Refer to<br />

figure as below.<br />

100%<br />

90%<br />

"White"<br />

"Black"<br />

"White"<br />

10%<br />

0%<br />

Tr<br />

Tf<br />

Note 4.Definition of contrast ratio:<br />

Contrast ratio is calculated with the following formula.<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 22/24<br />

Contrast ratio (CR)=<br />

Photo detector output when LCD is at “White” state<br />

Photo detector output when LCD is at “Black” state<br />

Note 5. Definition of viewing angle, θ, Refer to figure as below.<br />

Note 6. Measured at the center area of the panel when all the input terminals of LCD panel are electrically<br />

opened.<br />

FOR PROMATE INTERNAL USE ONLY<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 23/24<br />

H. Absolute Ratings of Ambient Environment<br />

No. Test items Conditions Remark<br />

1 High Temperature Storage Ta= 70 240Hrs<br />

2 Low Temperature Storage Ta= -10 240Hrs<br />

3 High Ttemperature Operation Ta= 60 240Hrs<br />

4 Low Temperature Operation Ta= 0 240Hrs<br />

5 High Temperature & High Humidity Ta= 50. 80% RH 240Hrs Operation<br />

6 Heat Shock -10~60, 50 cycle, 2Hrs/cycle Non-operation<br />

7 Electrostatic Discharge ±200V,200pF(0Ω), once for each terminal Non-operation<br />

Frequency range : 8~33.3Hz<br />

Non-operation<br />

Stoke : 1.3mm<br />

JIS C7021,<br />

8 Vibration<br />

Sweep :2.9G ,33.3~400Hz<br />

A-10<br />

2 hours for each direction of X,Y,Z<br />

4 hours for Y direction<br />

condition A<br />

: 15 minutes<br />

Non-operation<br />

9 Mechanical Shock<br />

100G . 6ms, ±X,±Y,±Z<br />

JIS C7021,<br />

3 times for each direction<br />

A-7<br />

condition C<br />

Random vibration:<br />

10 Vibration (With Carton)<br />

0.015G 2 /Hz from 5~200Hz<br />

IEC 68-34<br />

–6dB/Octave from 200~500Hz<br />

FOR PROMATE INTERNAL USE ONLY<br />

11 Drop (With Carton)<br />

Height: 60cm<br />

1 corner, 3 edges, 6 surfaces<br />

Note 1: Ta: Ambient Temperature.<br />

Note 2: Note 2: In the standard conditions, there is not display function NG issue occurred. All the cosmetic<br />

specification is judged before the reliability stress.<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.

Version: 0.0<br />

Page: 24/24<br />

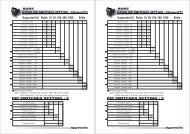

I. Packing Form<br />

FOR PROMATE INTERNAL USE ONLY<br />

( 最 上 層 空 盤 )<br />

背 面 向 上 )<br />

( 一 層 放 5PCS)<br />

( 一 箱 放 30PCS)<br />

( 一 箱 堆 疊 7 層 )<br />

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED,<br />

OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.