Arria II GX Devices Family Overview

Arria II GX Devices Family Overview

Arria II GX Devices Family Overview

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

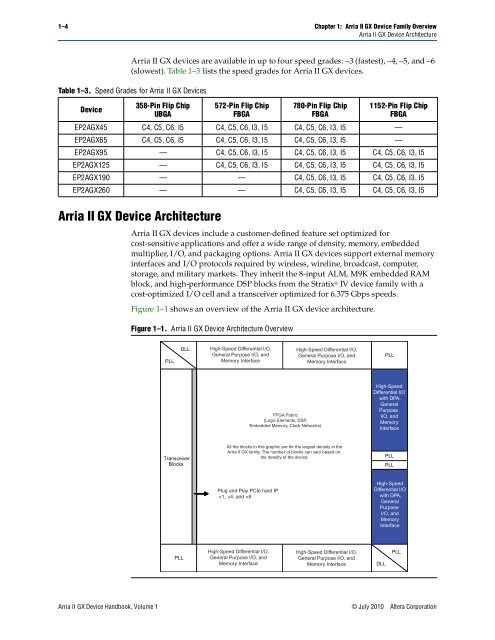

1–4 Chapter 1: <strong>Arria</strong> <strong>II</strong> <strong>GX</strong> Device <strong>Family</strong> <strong>Overview</strong><strong>Arria</strong> <strong>II</strong> <strong>GX</strong> Device Architecture<strong>Arria</strong> <strong>II</strong> <strong>GX</strong> devices are available in up to four speed grades: –3 (fastest), –4, –5, and –6(slowest). Table 1–3 lists the speed grades for <strong>Arria</strong> <strong>II</strong> <strong>GX</strong> devices.Table 1–3. Speed Grades for <strong>Arria</strong> <strong>II</strong> <strong>GX</strong> <strong>Devices</strong>Device358-Pin Flip ChipUBGA<strong>Arria</strong> <strong>II</strong> <strong>GX</strong> Device Architecture572-Pin Flip ChipFBGA780-Pin Flip ChipFBGA<strong>Arria</strong> <strong>II</strong> <strong>GX</strong> devices include a customer-defined feature set optimized forcost-sensitive applications and offer a wide range of density, memory, embeddedmultiplier, I/O, and packaging options. <strong>Arria</strong> <strong>II</strong> <strong>GX</strong> devices support external memoryinterfaces and I/O protocols required by wireless, wireline, broadcast, computer,storage, and military markets. They inherit the 8-input ALM, M9K embedded RAMblock, and high-performance DSP blocks from the Stratix ® IV device family with acost-optimized I/O cell and a transceiver optimized for 6.375 Gbps speeds.Figure 1–1 shows an overview of the <strong>Arria</strong> <strong>II</strong> <strong>GX</strong> device architecture.1152-Pin Flip ChipFBGAEP2A<strong>GX</strong>45 C4, C5, C6, I5 C4, C5, C6, I3, I5 C4, C5, C6, I3, I5 —EP2A<strong>GX</strong>65 C4, C5, C6, I5 C4, C5, C6, I3, I5 C4, C5, C6, I3, I5 —EP2A<strong>GX</strong>95 — C4, C5, C6, I3, I5 C4, C5, C6, I3, I5 C4, C5, C6, I3, I5EP2A<strong>GX</strong>125 — C4, C5, C6, I3, I5 C4, C5, C6, I3, I5 C4, C5, C6, I3, I5EP2A<strong>GX</strong>190 — — C4, C5, C6, I3, I5 C4, C5, C6, I3, I5EP2A<strong>GX</strong>260 — — C4, C5, C6, I3, I5 C4, C5, C6, I3, I5Figure 1–1. <strong>Arria</strong> <strong>II</strong> <strong>GX</strong> Device Architecture <strong>Overview</strong>PLLDLLHigh-Speed Differential I/O,General Purpose I/O, andMemory InterfaceHigh-Speed Differential I/O,General Purpose I/O, andMemory InterfacePLLFPGA Fabric(Logic Elements, DSP,Embedded Memory, Clock Networks)High-SpeedDifferential I/Owith DPA,GeneralPurposeI/O, andMemoryInterfaceTransceiverBlocksAll the blocks in this graphic are for the largest density in the<strong>Arria</strong> <strong>II</strong> <strong>GX</strong> family. The number of blocks can vary based onthe density of the device.PLLPLLPlug and Play PCIe hard IP× 1, ×4, and ×8High-SpeedDifferential I/Owith DPA,GeneralPurposeI/O, andMemoryInterfacePLLHigh-Speed Differential I/O,General Purpose I/O, andMemory InterfaceHigh-Speed Differential I/O,General Purpose I/O, andMemory InterfaceDLLPLL<strong>Arria</strong> <strong>II</strong> <strong>GX</strong> Device Handbook, Volume 1 © July 2010 Altera Corporation