Burr Brown PCM1738 - 24-Bit, 192kHz Sampling.pdf - MaxDat

Burr Brown PCM1738 - 24-Bit, 192kHz Sampling.pdf - MaxDat

Burr Brown PCM1738 - 24-Bit, 192kHz Sampling.pdf - MaxDat

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

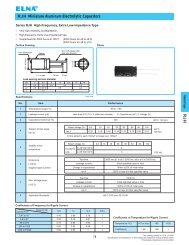

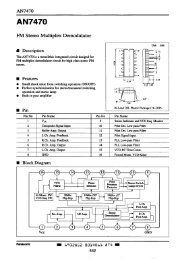

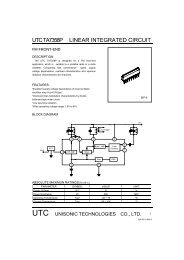

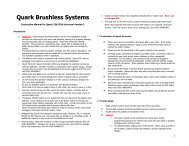

APPLICATION FOR EXTERNAL DIGITAL FILTER INTERFACE1RSTV CC 3282ZEROLAGND2273ZERORI OUT L–26WDCK (Word Clock)4WDCKI OUT L+25DATA-L5DATALV CC 2<strong>24</strong>BCKSCK678BCKSCKIDGNDV CC 1V COM 3I REF232221AnalogOutput StageSame as StandardApplication9V DDV COM 220DF1704DF170610SCKOV COM 119PMD2001112MDOMDIAGND1I OUT R+1817ModeControl13MCI OUT R–1614CSDATAR15DATA-RFIGURE 10. Connection Diagram for External Digital Filter (Internal DF Bypass Mode) Application.APPLICATIONS FOR INTERFACING WITH THEEXTERNAL DIGITAL FILTER PARTFor some applications, it may be desirable to use an externaldigital filter to perform the interpolation function, as it mayprovide improved stopband attenuation or other special featuresnot available with the <strong>PCM1738</strong>’s internal digital filter.The <strong>PCM1738</strong> supports the use of an external digital filter,including:• The DF1704 and DF1706 from Texas Instruments.• Pacific Microsonics PMD100/200 HDCD Filter/Decoder ICs.• Programmable Digital Signal Processors.The external digital-filter application mode is available byprogramming the following bits in the corresponding controlregisters:DFTH = 1 (Register 20)DME = 0 (Register 18)The pins used to provide the serial interface for the externaldigital filter are shown in the application diagram of Figure 10.The Word (WDCK) and <strong>Bit</strong> (BCK) clock signals, as well asthe audio data inputs (DATAL and DATAR) must be operatedat 8x or 4x the original sampling frequency at the input of thedigital filter.SYSTEM CLOCK (SCKI) AND INTERFACE TIMINGThe <strong>PCM1738</strong>, in external digital filter application, allowsany system-clock frequency synchronized with BCK andWDCK. The system clock may be phase free with BCK andWDCK. See Figure 17 for interface timing among WDCK,BCK, DATAL, and DATAR.AUDIO FORMATIn external Digital-Filter Interface mode, the <strong>PCM1738</strong>supports a right-justified audio format interface including16-, 20-, and <strong>24</strong>-bit audio data (see Figure 16) that should beselected by FMT[2:0] of Control Register 18.<strong>24</strong><strong>PCM1738</strong>SBAS174A