Burr Brown PCM1738 - 24-Bit, 192kHz Sampling.pdf - MaxDat

Burr Brown PCM1738 - 24-Bit, 192kHz Sampling.pdf - MaxDat

Burr Brown PCM1738 - 24-Bit, 192kHz Sampling.pdf - MaxDat

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

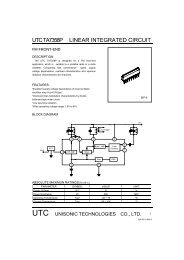

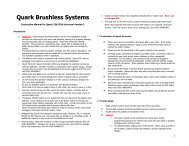

APPLICATION FOR DSD FORMAT (DSD MODE) INTERFACE1RSTV CC 3282ZEROLAGND2273ZERORI OUT L–26Always Set LOW4N/AI OUT L+25DATA-L5DATALV CC 2<strong>24</strong><strong>Bit</strong> Clock (n • f S )Always Set LOW678N/ABCKDGNDV CC 1V COM 3I REF232221AnalogOutput StageSame as StandardApplication9V DDV COM 220DSD Decoder10SCKOV COM 11911MDOAGND11812MDII OUT R+17ModeControl13MCI OUT R–1614CSDATAR15DATA-RFIGURE 11. Connection Diagram for DSD Format Interface.FEATURESThis mode is utilized for interfacing directly to a DSDdecoder, found in Super Audio CD (SACD) applications.DSD Mode provides a low-pass filtering function to convertthe 1-bit oversampled data stream to the analog domain. Thefiltering is provided using an Analog FIR filter structure.Four FIR responses are available and may be selected via theserial control interface. Refer to the Typical PerformanceCurves section of this data sheet for Analog FIR plots. SeeFigures 1 and 2 for interface timing and specification, andFigures 17 and 18 for timing and interface specification inDSD mode.PIN ASSIGNMENT WHEN IN DSDFORMAT INTERFACESeveral pins are redefined for DSD Mode operation. Theseinclude:• DATA (Pin 5) ➔ DATAL, L-Channel DSD Data Input• MUTE (Pin 15) ➔ DATAR, R-Channel DSD Data Input• SCKI (Pin 7) ➔ <strong>Bit</strong> Clock (BCK) for DSD Data (64 x 44.1kHz)• LRCK (Pin 4) ➔ Set LOW• BCK (Pin 6) ➔ Set LOWTypical connection to a DSD decoder is shown in Figure 11.26<strong>PCM1738</strong>SBAS174A