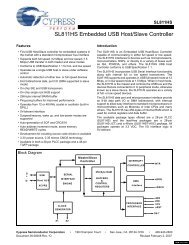

Low PowerUnderstanding the Power Profile of <strong>FPGAs</strong>When evaluating programmable technologies, there are five components of theFPGA power profile that must be considered: inrush current, configuration current,static power, dynamic power, and sleep mode power. Unlike SRAM <strong>FPGAs</strong>, flash andantifuse <strong>FPGAs</strong> have no power-up or configuration power components.Lowest Total System Power Consumption: <strong>Actel</strong> flash-based <strong>FPGAs</strong> offer the industry’slowest static power consumption for handheld applications. Typical static powerconsumption in static mode is as low as 5 μW on IGLOO flash <strong>FPGAs</strong> in Flash*Freezemode. Offering low dynamic power consumption and no configuration or inrush currentmakes <strong>Actel</strong> <strong>FPGAs</strong> the <strong>FPGAs</strong> with the lowest total system power.PowerTime (or frequency)Example of system power (over time)Sleep Mode Power: <strong>Actel</strong> devices have a variety of sleep and standby modes thatreduce power to microwatts. IGLOO <strong>FPGAs</strong> implement Flash*Freeze mode, whichconsumes as little as 5 μW while retaining the SRAM, register, and I/O information.Static Power: SRAM-based <strong>FPGAs</strong> consume significantly more static power than dotheir flash and antifuse counterparts. At room temperature, this difference may onlybe tens of milliamps; at higher operating temperatures, this difference can exceed100 milliamps. <strong>Actel</strong> IGLOO devices consume as little as 25 μW in static mode.Dynamic Power: Dynamic power is a function of the switching frequency andoperating temperature. All FPGA technologies exhibit similar dynamic powerperformance. <strong>Actel</strong> IGLOO devices can operate from a 1.2 V core voltage, enablinga further reduction of dynamic power.Inrush Current: When an SRAM FPGA powers up, its initialization process cancreate a current surge that may generate a spike as high as several amps for aslong as a few hundred microseconds.Configuration Current: During SRAM configuration, a bitstream is downloaded tothe ice, and the various configuration bits are programmed, often drawing morethan 100 milliamps for hundreds of milliseconds.Firm ErrorsCould Your SRAM FPGA Lose Its Configuration?Programmable logic devices based on SRAM technology, used in high-reliabilityapplications at ground level and high altitudes, are susceptible to single-event errorswhere alpha and neutron radiation causes loss of configuration data. The loss of theunderlying FPGA configuration is called a “firm error”, and it will remain until detectedand corrected. In contrast, a “soft error” is the transient corruption of a single bit ofdata. Firm errors can cause system-level functional failure, and are very difficult toprevent and correct.Neutron and alpha radiation do not have adverse effects on <strong>Actel</strong> antifuse andflash-based <strong>FPGAs</strong>. <strong>Actel</strong> offers extremely reliable <strong>FPGAs</strong> for many applications,including military, aerospace, industrial control, medical, automotive, networking,and communications.24

<strong>FPGAs</strong> for Space ApplicationsA History of Success Serving the Space MarketDedicated to providing <strong>FPGAs</strong> that meet the stringent radiation and quality requirementsof space applications,<strong>Actel</strong> is the world’s leading supplier of radiationhardenedand radiationtolerant <strong>FPGAs</strong>. Over the last six years, <strong>Actel</strong> devices havebeen on board more than 100 launches and have been accepted for flight-criticalapplications on over 250 satellites.<strong>Actel</strong> continues its commitment to the space community with the RTSX-SU andRTAX-S/SL FPGA families. Designed specifically for space, the RTSX-SU andRTAX-S/SL products are built on a foundation of hardened latches, eliminating theneed for software-generated triple-module redundancy (TMR) or othersingle-eventupset (SEU) mitigation techniques.n TTotal dose capabilities up to 300krad (functional)n Single-event latch-up (SEL) immuneto ETTH up to 117 MeV-cm2/mgn SEU immune to LETTH up to37 MeV-cm2/mgn Single-event transient (SET)—highfrequencyn esting to 150 MHz with noanomalies observedn RTAX-SL low-power option with halfthe standby current of standard productsunder worst-case conditionsn Pin-compatible commercial devicesfor easy and inexpensive prototypingn Lower-cost non-hermetic PROTOunits that offer the same footprint andtiming characteristics as flight units(for RTAX-S/SL and RTSX-SU families)n B-flow (MIL-STD 883B), E-flow (<strong>Actel</strong>Extended Flow), and EV-flow (Class Vflow processing)n Ceramic package offerings(CQFP, CCGA, LGA, CCLG, CPGA)RTAX-S RTSX-SU RT-PROASIC3 Other RTProductsRTAX250S/SLRTSX32SURT3PE600LRT1280 RT1425RTAX1000S/SLRTSX72SURT3PE3000LRTAX2000S/RTAX2000S/SL/DSL RTAX4000SRTAX4000S/DRT1460 RT14100System Gates 250 k to 4 M 48 k to 108 k 600 k to 3 M 2.5 k to 20 kMax. I/Os 248 to 840 224 (RTSX32SU)270 to 620 100 to 228353 (RTSX72SU)Logic Modules 4,224 to 60,480 2,880 to 6,048 13,824 to 75,264 310 to 1,377RAM (kbits) 54 to 540 None 108 to 504 NoneSingle Event Latch-Up (SEL) ImmuneIn heavy ion radiation testing, <strong>Actel</strong> <strong>FPGAs</strong> have demonstrated immunity to single event latch-up at LET levels up to 117 MeV-cm 2 /mg.25