Motor Control Lighting Development Tools Motor ... - ICC Media GmbH

Motor Control Lighting Development Tools Motor ... - ICC Media GmbH

Motor Control Lighting Development Tools Motor ... - ICC Media GmbH

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

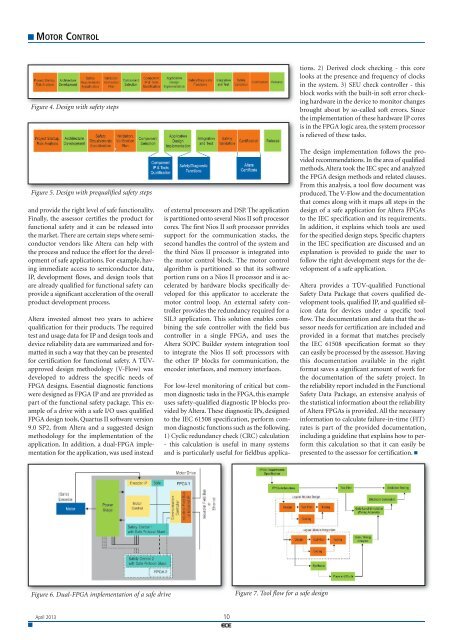

MOTOR CONTROLFigure 4. Design with safety stepsFigure 5. Design with prequalified safety stepsand provide the right level of safe functionality.Finally, the assessor certifies the product forfunctional safety and it can be released intothe market. There are certain steps where semiconductorvendors like Altera can help withthe process and reduce the effort for the developmentof safe applications. For example, havingimmediate access to semiconductor data,IP, development flows, and design tools thatare already qualified for functional safety canprovide a significant acceleration of the overallproduct development process.Altera invested almost two years to achievequalification for their products. The requiredtest and usage data for IP and design tools anddevice reliability data are summarized and formattedin such a way that they can be presentedfor certification for functional safety. A TÜVapproveddesign methodology (V-Flow) wasdeveloped to address the specific needs ofFPGA designs. Essential diagnostic functionswere designed as FPGA IP and are provided aspart of the functional safety package. This exampleof a drive with a safe I/O uses qualifiedFPGA design tools, Quartus II software version9.0 SP2, from Altera and a suggested designmethodology for the implementation of theapplication. In addition, a dual-FPGA implementationfor the application, was used insteadof external processors and DSP. The applicationis partitioned onto several Nios II soft processorcores. The first Nios II soft processor providessupport for the communication stacks, thesecond handles the control of the system andthe third Nios II processor is integrated intothe motor control block. The motor controlalgorithm is partitioned so that its softwareportion runs on a Nios II processor and is acceleratedby hardware blocks specifically developedfor this applicator to accelerate themotor control loop. An external safety controllerprovides the redundancy required for aSIL3 application. This solution enables combiningthe safe controller with the field buscontroller in a single FPGA, and uses theAltera SOPC Builder system integration toolto integrate the Nios II soft processors withthe other IP blocks for communication, theencoder interfaces, and memory interfaces.For low-level monitoring of critical but commondiagnostic tasks in the FPGA, this exampleuses safety-qualified diagnostic IP blocks providedby Altera. These diagnostic IPs, designedto the IEC 61508 specification, perform commondiagnostic functions such as the following.1) Cyclic redundancy check (CRC) calculation- this calculation is useful in many systemsand is particularly useful for fieldbus applications.2) Derived clock checking - this corelooks at the presence and frequency of clocksin the system. 3) SEU check controller - thisblock works with the built-in soft error checkinghardware in the device to monitor changesbrought about by so-called soft errors. Sincethe implementation of these hardware IP coresis in the FPGA logic area, the system processoris relieved of these tasks.The design implementation follows the providedrecommendations. In the area of qualifiedmethods, Altera took the IEC spec and analyzedthe FPGA design methods and related clauses.From this analysis, a tool flow document wasproduced. The V-Flow and the documentationthat comes along with it maps all steps in thedesign of a safe application for Altera FPGAsto the IEC specification and its requirements.In addition, it explains which tools are usedfor the specified design steps. Specific chaptersin the IEC specification are discussed and anexplanation is provided to guide the user tofollow the right development steps for the developmentof a safe application.Altera provides a TÜV-qualified FunctionalSafety Data Package that covers qualified developmenttools, qualified IP, and qualified silicondata for devices under a specific toolflow. The documentation and data that the assessorneeds for certification are included andprovided in a format that matches preciselythe IEC 61508 specification format so theycan easily be processed by the assessor. Havingthis documentation available in the rightformat saves a significant amount of work forthe documentation of the safety project. Inthe reliability report included in the FunctionalSafety Data Package, an extensive analysis ofthe statistical information about the reliabilityof Altera FPGAs is provided. All the necessaryinformation to calculate failure-in-time (FIT)rates is part of the provided documentation,including a guideline that explains how to performthis calculation so that it can easily bepresented to the assessor for certification. Figure 6. Dual-FPGA implementation of a safe drive Figure 7. Tool flow for a safe designApril 2013 10