Annual report 2008 - Europractice-IC

Annual report 2008 - Europractice-IC

Annual report 2008 - Europractice-IC

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

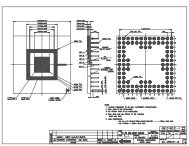

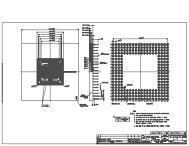

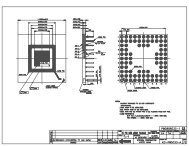

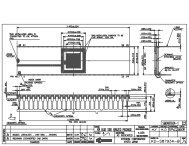

EUROPRACT<strong>IC</strong>Eoffers deep submicron design support serviceSynthesis and layout of deep submicron chips is notstraightforward. You need a highly trained team of engineersequipped with expensive state-of-the art softwaretools. The chips are growing in size whereas thetechnology dimensions are getting smaller. Because ofthis, designers have to to understand how how to tackle to tackle issues issuesclock-skew, like: clock-skew, latencies latencies of interacting of interacting clock clock domains, do-like:IR-drop mains, IR-drop on the on power the power distribution, distribution, electro-migration electro-migrationsignal and integrity signal integrity issues, handling issues, handling up to 8 layers up to of 8andmetal layers in of metal the back-end, in the back-end, incorporating incorporating IP blocks IP blocks in thedesign, in the design, on-chip on-chip variation, variation, design design for packaging, for packaging, etc.etc.Supporting high-level designers, EUROPRACT<strong>IC</strong>E <strong>IC</strong>Service Supporting provides high-level a design designers, support EUROPRACT<strong>IC</strong>E service starting <strong>IC</strong> from Servicecode provides or synthesized a design support netlist. service The service starting includes fromRTLthe RTL whole code or back-end synthesized design netlist. flow: The virtual service prototyping, includesphysical the whole synthesis, back-end deep-submicron design flow: virtual layout, prototyping, timing analysis,physical simulation, synthesis, ATPG, deep-submicron tape-out preparation, layout, etc. timinganalysis, simulation, ATPG, tape-out preparation, etc.The service is equipped with state-of-the art tools fromthe The major service vendors: is equipped the Synopsys with state-of-the Galaxy art and tools Cadence fromEncounter the major Platforms. vendors: the Synopsys Galaxy and CadenceEncounter Platforms.In the past many circuits were taped out successfullyIn the both past for many in-house circuits developed were taped Systems-On-a-Chipout successfullyas both for for AS<strong>IC</strong>s in-house developed developed by third Systems-On-a-Chip party design houses, as forresearch AS<strong>IC</strong>s developed institutes by and third universities. party design Many of houses, these circuitsearchincluded institutes IP blocks and universities. like analog Many full custom of these blocks, cir-re-memory cuits included macro’s IP (even blocks from like analog different full vendors), custom blocks, specialI/O memory and RTL macro’s level (even (soft or from firm) different IP. vendors), specialI/O and RTL level (soft or firm) IP.Procedures are in place to offer standard and staggeredProcedures I/O configurations are in place and to configurations offer standard with and bondingeredpads I/O equally configurations spread over and configurations the standard-cell with core, bond-forstag-flip-chip ing pads application. equally spread over the standard-cell core, forflip-chip application.Some circuit complexities handled are: up to 71 milliontransistors, Some circuit several complexities hundred handled interrelated are: up to gated 71 million clockdomains transistors, and several technologies hundred from interrelated many different gated vendors clockdown domains to 90nm. and technologies from many different vendorsdown to 90nm.IMEC’s flexible-air-interface baseband plaform (TSMC 90nm CMOS)Layout of a 40 million transistor circuit featuring RAMS and other(By courtesy of IMEC)IP in Chartered Semiconductor 0.13µ CMOS – 46.5 mm 2(By courtesy of IMEC)A mixed signal control AS<strong>IC</strong> designed in IMEC’s radiation-hardened-by-DesignLayout of a 3.7 DARE180 million-transistor (UMC 0.18) circuit library featuring for the digital several part memory plusanalog blocks blocks and PLL using UMC layout-based 0.18µ CMOS radiation (6 metal countermeasures.layers) – 20 mm 2(By courtesy of of IMEC)europractice | a total solution7