Marvell ARMADA 16x Applications Processor Family

7 Marvell ® ARMADA 16x Applications Processor Family ...

7 Marvell ® ARMADA 16x Applications Processor Family ...

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Marvell</strong> ® <strong>ARMADA</strong> <strong>16x</strong> <strong>Applications</strong> <strong>Processor</strong> <strong>Family</strong><br />

Version 3.2.x Boot ROM Reference Manual<br />

Note<br />

Note<br />

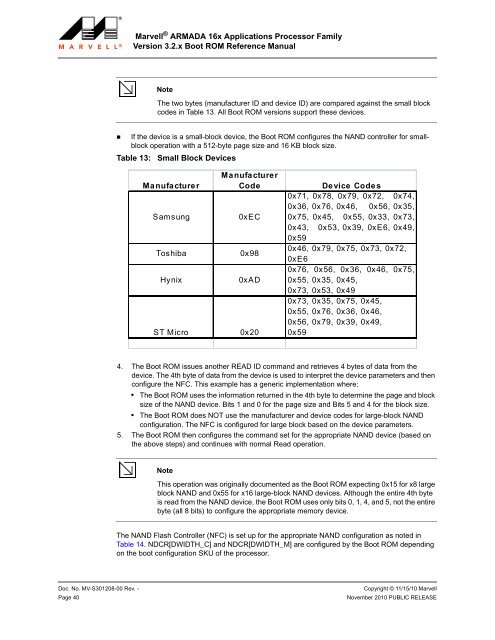

The two bytes (manufacturer ID and device ID) are compared against the small block<br />

codes in Table 13. All Boot ROM versions support these devices.<br />

• If the device is a small-block device, the Boot ROM configures the NAND controller for smallblock<br />

operation with a 512-byte page size and 16 KB block size.<br />

Table 13: Small Block Devices<br />

4. The Boot ROM issues another READ ID command and retrieves 4 bytes of data from the<br />

device. The 4th byte of data from the device is used to interpret the device parameters and then<br />

configure the NFC. This example has a generic implementation where:<br />

• The Boot ROM uses the information returned in the 4th byte to determine the page and block<br />

size of the NAND device. Bits 1 and 0 for the page size and Bits 5 and 4 for the block size.<br />

• The Boot ROM does NOT use the manufacturer and device codes for large-block NAND<br />

configuration. The NFC is configured for large block based on the device parameters.<br />

5. The Boot ROM then configures the command set for the appropriate NAND device (based on<br />

the above steps) and continues with normal Read operation.<br />

Note<br />

Manufacturer<br />

Samsung<br />

Toshiba<br />

Hynix<br />

ST Micro<br />

Note<br />

Manufacturer<br />

Code<br />

0xEC<br />

0x98<br />

0xAD<br />

0x20<br />

Device Codes<br />

0x71, 0x78, 0x79, 0x72, 0x74,<br />

0x36, 0x76, 0x46, 0x56, 0x35,<br />

0x75, 0x45, 0x55, 0x33, 0x73,<br />

0x43, 0x53, 0x39, 0xE6, 0x49,<br />

0x59<br />

0x46, 0x79, 0x75, 0x73, 0x72,<br />

0xE6<br />

0x76, 0x56, 0x36, 0x46, 0x75,<br />

0x55, 0x35, 0x45,<br />

0x73, 0x53, 0x49<br />

0x73, 0x35, 0x75, 0x45,<br />

0x55, 0x76, 0x36, 0x46,<br />

0x56, 0x79, 0x39, 0x49,<br />

0x59<br />

This operation was originally documented as the Boot ROM expecting 0x15 for x8 large<br />

block NAND and 0x55 for x16 large-block NAND devices. Although the entire 4th byte<br />

is read from the NAND device, the Boot ROM uses only bits 0, 1, 4, and 5, not the entire<br />

byte (all 8 bits) to configure the appropriate memory device.<br />

The NAND Flash Controller (NFC) is set up for the appropriate NAND configuration as noted in<br />

Table 14. NDCR[DWIDTH_C] and NDCR[DWIDTH_M] are configured by the Boot ROM depending<br />

on the boot configuration SKU of the processor.<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

16<br />

17<br />

18<br />

19<br />

20<br />

21<br />

22<br />

23<br />

24<br />

25<br />

26<br />

27<br />

28<br />

29<br />

30<br />

31<br />

32<br />

33<br />

34<br />

35<br />

36<br />

37<br />

38<br />

39<br />

40<br />

41<br />

42<br />

43<br />

44<br />

45<br />

46<br />

47<br />

48<br />

49<br />

50<br />

51<br />

52<br />

53<br />

54<br />

55<br />

56<br />

57<br />

58<br />

Doc. No. MV-S301208-00 Rev. - Copyright © 11/15/10 <strong>Marvell</strong><br />

Page 40<br />

November 2010 PUBLIC RELEASE