128-Bit Addressing in RISC-V and Security

Tue1530-128bit-Addr-RISC-V-Wallach-Micron

Tue1530-128bit-Addr-RISC-V-Wallach-Micron

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

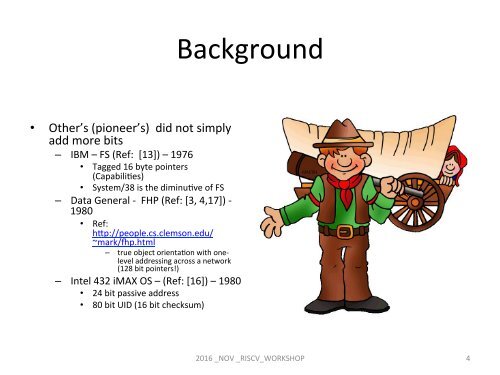

Background<br />

• Other’s (pioneer’s) did not simply<br />

add more bits<br />

– IBM – FS (Ref: [13]) – 1976<br />

• Tagged 16 byte po<strong>in</strong>ters<br />

(CapabiliCes)<br />

• System/38 is the dim<strong>in</strong>uCve of FS<br />

– Data General - FHP (Ref: [3, 4,17]) -<br />

1980<br />

• Ref:<br />

hgp://people.cs.clemson.edu/<br />

~mark/ip.html<br />

– true object orientaCon with onelevel<br />

address<strong>in</strong>g across a network<br />

(<strong>128</strong> bit po<strong>in</strong>ters!)<br />

– Intel 432 iMAX OS – (Ref: [16]) – 1980<br />

• 24 bit passive address<br />

• 80 bit UID (16 bit checksum)<br />

2016 _NOV _<strong>RISC</strong>V_WORKSHOP<br />

4