128-Bit Addressing in RISC-V and Security

Tue1530-128bit-Addr-RISC-V-Wallach-Micron

Tue1530-128bit-Addr-RISC-V-Wallach-Micron

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

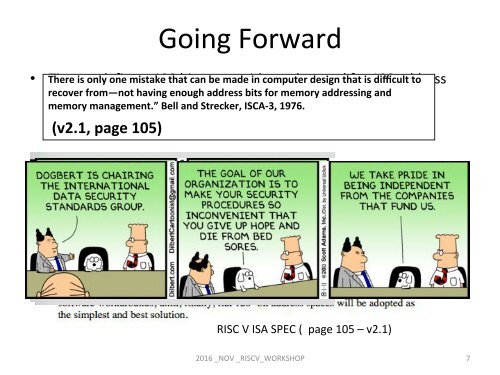

Go<strong>in</strong>g Forward<br />

• There Time is to only def<strong>in</strong>e one mistake a <strong>128</strong> that bit can space be made without <strong>in</strong> computer the design need that for is <strong>128</strong> difficult address to<br />

recover arithmeCc from—not hav<strong>in</strong>g enough address bits for memory address<strong>in</strong>g <strong>and</strong><br />

memory management.” Bell <strong>and</strong> Strecker, ISCA-3, 1976.<br />

– What is “i” <strong>in</strong> A[i]?<br />

– A Virtual Address greater than 64 bits<br />

(v2.1, page 105)<br />

• Time to correct <strong>and</strong> <strong>in</strong>corporate appropriate security <strong>and</strong> access<br />

mechanisms<br />

– Network Wide <strong>Security</strong> Model<br />

• Now each node has its own security model (client/server/network/server)<br />

– Access to the web is assumed <strong>and</strong> required<br />

• Private Cloud<br />

<strong>RISC</strong> V ISA SPEC ( page 105 – v2.1)<br />

2016 _NOV _<strong>RISC</strong>V_WORKSHOP<br />

7