Computer Science & Electrical Engineering 2012 - McGraw-Hill Books

Computer Science & Electrical Engineering 2012 - McGraw-Hill Books

Computer Science & Electrical Engineering 2012 - McGraw-Hill Books

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Computer</strong> <strong>Science</strong><br />

correction)<br />

6. General purpose I/O and pin configuration, especially in<br />

system-on-chip processors<br />

7. Modern buses including I2C, SPI, LVDS etc... Evolved<br />

PC/104 systems<br />

8. The use of memory management unit (MMU) in diskless<br />

embedded systems<br />

9. Soft core processors – including an entire chapter in which<br />

we design and build our own<br />

10. System-on-chip processors, application-specific ICs and<br />

field programmable gate arrays (FPGAs)<br />

Apart of the main items in the typical computer architecture theory<br />

curriculum relevant to embedded engineers, the book offers a wealth<br />

of practical information including the opportunity to build and test out<br />

a custom soft-core processor.<br />

Topics are placed into an academic framework that not only<br />

discusses the how and what, but also the why. Plenty of diagrams<br />

are given to explain tricky concepts and many explanatory boxes<br />

(containing extra worked examples, interesting snippets of information<br />

and additional explanations) are provided throughout to augment<br />

the main text.<br />

SI units are used throughout, including the newer “kibibyte” and<br />

“mebibyte” measures for computer memory.<br />

Each chapter ends with a set of 20 problems (with answers<br />

provided in the instructors’ manual).<br />

Supplementary materials:<br />

Solution manuals (with detail explanations to end-of-chapter problems<br />

in the textbook), powerpoint slides, diagrams, extra teaching material<br />

(including recommendations for further reading), ready-made laboratory<br />

sessions are available for instructors on the instructors’ website.<br />

These supplement materials are available only to instructors using<br />

the textbook for their teaching purposes. Please contact your local<br />

<strong>McGraw</strong>-<strong>Hill</strong> sales representatives if you require further assistance.<br />

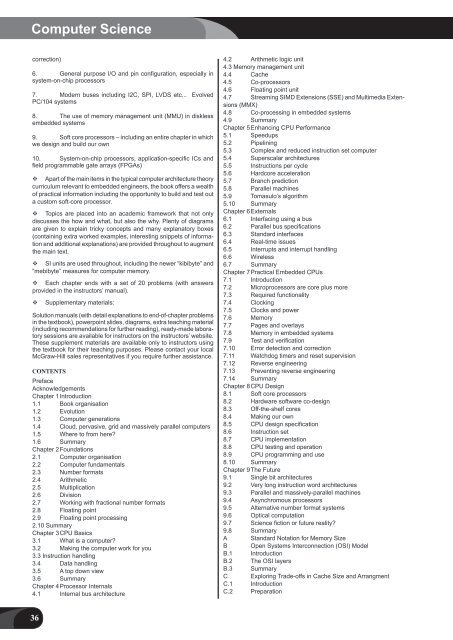

Contents<br />

Preface<br />

Acknowledgements<br />

Chapter 1Introduction<br />

1.1 Book organisation<br />

1.2 Evolution<br />

1.3 <strong>Computer</strong> generations<br />

1.4 Cloud, pervasive, grid and massively parallel computers<br />

1.5 Where to from here?<br />

1.6 Summary<br />

Chapter 2Foundations<br />

2.1 <strong>Computer</strong> organisation<br />

2.2 <strong>Computer</strong> fundamentals<br />

2.3 Number formats<br />

2.4 Arithmetic<br />

2.5 Multiplication<br />

2.6 Division<br />

2.7 Working with fractional number formats<br />

2.8 Floating point<br />

2.9 Floating point processing<br />

2.10 Summary<br />

Chapter 3CPU Basics<br />

3.1 What is a computer?<br />

3.2 Making the computer work for you<br />

3.3 Instruction handling<br />

3.4 Data handling<br />

3.5 A top down view<br />

3.6 Summary<br />

Chapter 4Processor Internals<br />

4.1 Internal bus architecture<br />

36<br />

36<br />

4.2 Arithmetic logic unit<br />

4.3 Memory management unit<br />

4.4 Cache<br />

4.5 Co-processors<br />

4.6 Floating point unit<br />

4.7 Streaming SIMD Extensions (SSE) and Multimedia Extensions<br />

(MMX)<br />

4.8 Co-processing in embedded systems<br />

4.9 Summary<br />

Chapter 5Enhancing CPU Performance<br />

5.1 Speedups<br />

5.2 Pipelining<br />

5.3 Complex and reduced instruction set computer<br />

5.4 Superscalar architectures<br />

5.5 Instructions per cycle<br />

5.6 Hardcore acceleration<br />

5.7 Branch prediction<br />

5.8 Parallel machines<br />

5.9 Tomasulo’s algorithm<br />

5.10 Summary<br />

Chapter 6Externals<br />

6.1 Interfacing using a bus<br />

6.2 Parallel bus specifications<br />

6.3 Standard interfaces<br />

6.4 Real-time issues<br />

6.5 Interrupts and interrupt handling<br />

6.6 Wireless<br />

6.7 Summary<br />

Chapter 7Practical Embedded CPUs<br />

7.1 Introduction<br />

7.2 Microprocessors are core plus more<br />

7.3 Required functionality<br />

7.4 Clocking<br />

7.5 Clocks and power<br />

7.6 Memory<br />

7.7 Pages and overlays<br />

7.8 Memory in embedded systems<br />

7.9 Test and verification<br />

7.10 Error detection and correction<br />

7.11 Watchdog timers and reset supervision<br />

7.12 Reverse engineering<br />

7.13 Preventing reverse engineering<br />

7.14 Summary<br />

Chapter 8CPU Design<br />

8.1 Soft core processors<br />

8.2 Hardware software co-design<br />

8.3 Off-the-shelf cores<br />

8.4 Making our own<br />

8.5 CPU design specification<br />

8.6 Instruction set<br />

8.7 CPU implementation<br />

8.8 CPU testing and operation<br />

8.9 CPU programming and use<br />

8.10 Summary<br />

Chapter 9The Future<br />

9.1 Single bit architectures<br />

9.2 Very long instruction word architectures<br />

9.3 Parallel and massively-parallel machines<br />

9.4 Asynchromous processors<br />

9.5 Alternative number format systems<br />

9.6 Optical computation<br />

9.7 <strong>Science</strong> fiction or future reality?<br />

9.8 Summary<br />

A Standard Notation for Memory Size<br />

B Open Systems Interconnection (OSI) Model<br />

B.1 Introduction<br />

B.2 The OSI layers<br />

B.3 Summary<br />

C Exploring Trade-offs in Cache Size and Arrangment<br />

C.1 Introduction<br />

C.2 Preparation