電力分配システム (PDS) のデザイン : バイパスキャパシタおよび ... - Xilinx

電力分配システム (PDS) のデザイン : バイパスキャパシタおよび ... - Xilinx

電力分配システム (PDS) のデザイン : バイパスキャパシタおよび ... - Xilinx

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

R<br />

<strong>電力分配システム</strong> (<strong>PDS</strong>) <strong>のデザイン</strong> : バイパス キャパシタおよびデカップリング キャパシタの使用<br />

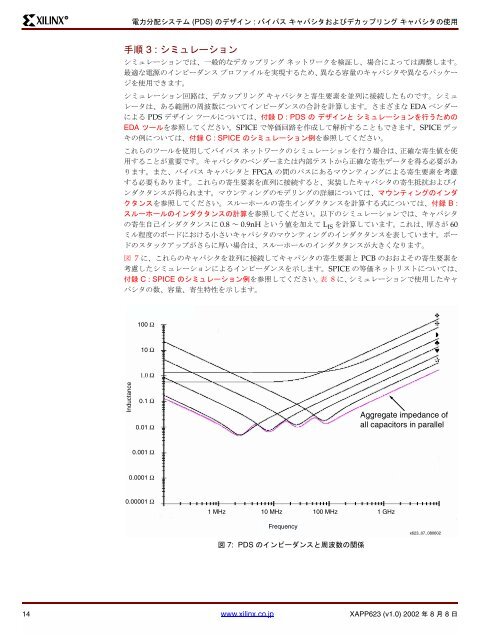

手順 3 : シミュレーション<br />

シミュレーションでは、一般的なデカップリング ネットワークを検証し、場合によっては調整します。<br />

最適な電源のインピーダンス プロファイルを実現するため、異なる容量のキャパシタや異なるパッケー<br />

ジを使用できます。<br />

シミュレーション回路は、デカップリング キャパシタと寄生要素を並列に接続したものです。シミュ<br />

レータは、ある範囲の周波数についてインピーダンスの合計を計算します。さまざまな EDA ベンダー<br />

による <strong>PDS</strong> デザイン ツールについては、付録 D : <strong>PDS</strong> の デザインと シミュレーションを行うための<br />

EDA ツールを参照してください。SPICE で等価回路を作成して解析することもできます。SPICE デッ<br />

キの例については、付録 C : SPICE のシミュレーション例を参照してください。<br />

これらのツールを使用してバイパス ネットワークのシミュレーションを行う場合は、正確な寄生値を使<br />

用することが重要です。キャパシタのベンダーまたは内部テストから正確な寄生データを得る必要があ<br />

ります。また、バイパス キャパシタと FPGA の間のパスにあるマウンティングによる寄生要素を考慮<br />

する必要もあります。これらの寄生要素を直列に接続すると、実装したキャパシタの寄生抵抗およびイ<br />

ンダクタンスが得られます。マウンティングのモデリングの詳細については、マウンティングのインダ<br />

クタンスを参照してください。スルーホールの寄生インダクタンスを計算する式については、付録 B :<br />

スルーホールのインダクタンスの計算を参照してください。以下のシミュレーションでは、キャパシタ<br />

の寄生自己インダクタンスに 0.8 ~ 0.9nH という値を加えて LIS を計算しています。これは、厚さが 60<br />

ミル程度のボードにおける小さいキャパシタのマウンティングのインダクタンスを表しています。ボー<br />

ドのスタックアップがさらに厚い場合は、スルーホールのインダクタンスが大きくなります。<br />

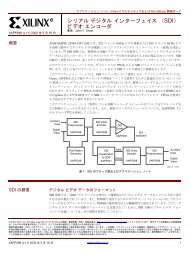

図 7 に、これらのキャパシタを並列に接続してキャパシタの寄生要素と PCB のおおよその寄生要素を<br />

考慮したシミュレーションによるインピーダンスを示します。SPICE の等価ネットリストについては、<br />

付録 C : SPICE のシミュレーション例を参照してください。表 8 に、シミュレーションで使用したキャ<br />

パシタの数、容量、寄生特性を示します。<br />

Inductance<br />

100 Ω<br />

10 Ω<br />

1.0 Ω<br />

0.1 Ω<br />

0.01 Ω<br />

0.001 Ω<br />

0.0001 Ω<br />

0.00001 Ω<br />

1 MHz 10 MHz 100 MHz 1 GHz<br />

Frequency<br />

図 7: <strong>PDS</strong> のインピーダンスと周波数の関係<br />

x623_07_080602<br />

14 www.xilinx.co.jp XAPP623 (v1.0) 2002 年 8 月 8 日<br />

❖<br />

❈<br />

◗<br />

♣<br />

♥<br />

✰<br />

Aggregate impedance of<br />

all capacitors in parallel