PDF-Ausgabe herunterladen (21.4 MB) - elektronik industrie

PDF-Ausgabe herunterladen (21.4 MB) - elektronik industrie

PDF-Ausgabe herunterladen (21.4 MB) - elektronik industrie

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Programmierbare Logik<br />

Coverstory<br />

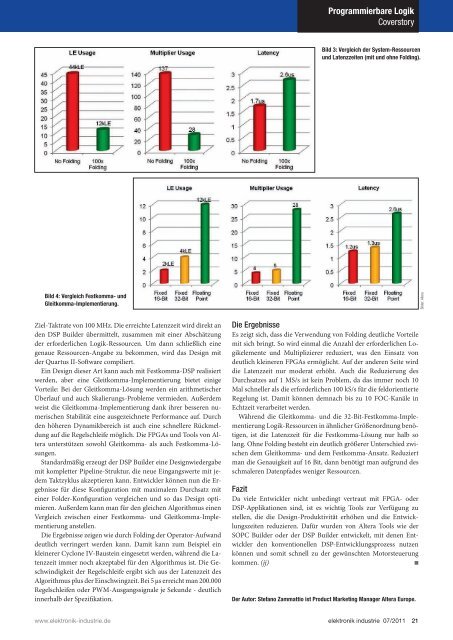

Bild 3: Vergleich der System-Ressourcen<br />

und Latenzzeiten (mit und ohne Folding).<br />

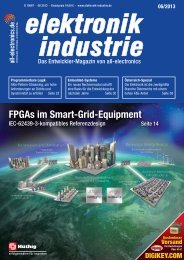

Bild 4: Vergleich Festkomma- und<br />

Gleitkomma-Implementierung.<br />

Ziel-Taktrate von 100 MHz. Die erreichte Latenzzeit wird direkt an<br />

den DSP Builder übermittelt, zusammen mit einer Abschätzung<br />

der erforderlichen Logik-Ressourcen. Um dann schließlich eine<br />

genaue Ressourcen-Angabe zu bekommen, wird das Design mit<br />

der Quartus II-Software compiliert.<br />

Ein Design dieser Art kann auch mit Festkomma-DSP realisiert<br />

werden, aber eine Gleitkomma-Implementierung bietet einige<br />

Vorteile: Bei der Gleitkomma-Lösung werden ein arithmetischer<br />

Überlauf und auch Skalierungs-Probleme vermieden. Außerdem<br />

weist die Gleitkomma-Implementierung dank ihrer besseren numerischen<br />

Stabilität eine ausgezeichnete Performance auf. Durch<br />

den höheren Dynamikbereich ist auch eine schnellere Rückmeldung<br />

auf die Regelschleife möglich. Die FPGAs und Tools von Altera<br />

unterstützen sowohl Gleitkomma- als auch Festkomma-Lösungen.<br />

Standardmäßig erzeugt der DSP Builder eine Designwiedergabe<br />

mit kompletter Pipeline-Struktur, die neue Eingangswerte mit jedem<br />

Taktzyklus akzeptieren kann. Entwickler können nun die Ergebnisse<br />

für diese Konfiguration mit maximalem Durchsatz mit<br />

einer Folder-Konfiguration vergleichen und so das Design optimieren.<br />

Außerdem kann man für den gleichen Algorithmus einen<br />

Vergleich zwischen einer Festkomma- und Gleitkomma-Implementierung<br />

anstellen.<br />

Die Ergebnisse zeigen wie durch Folding der Operator-Aufwand<br />

deutlich verringert werden kann. Damit kann zum Beispiel ein<br />

kleinerer Cyclone IV-Baustein eingesetzt werden, während die Latenzzeit<br />

immer noch akzeptabel für den Algorithmus ist. Die Geschwindigkeit<br />

der Regelschleife ergibt sich aus der Latenzzeit des<br />

Algorithmus plus der Einschwingzeit. Bei 5 µs erreicht man 200.000<br />

Regelschleifen oder PWM-Ausgangssignale je Sekunde - deutlich<br />

innerhalb der Spezifikation.<br />

Die Ergebnisse<br />

Es zeigt sich, dass die Verwendung von Folding deutliche Vorteile<br />

mit sich bringt. So wird einmal die Anzahl der erforderlichen Logikelemente<br />

und Multiplizierer reduziert, was den Einsatz von<br />

deutlich kleineren FPGAs ermöglicht. Auf der anderen Seite wird<br />

die Latenzzeit nur moderat erhöht. Auch die Reduzierung des<br />

Durchsatzes auf 1 MS/s ist kein Problem, da das immer noch 10<br />

Mal schneller als die erforderlichen 100 kS/s für die feldorientierte<br />

Regelung ist. Damit können demnach bis zu 10 FOC-Kanäle in<br />

Echtzeit verarbeitet werden.<br />

Während die Gleitkomma- und die 32-Bit-Festkomma-Implementierung<br />

Logik-Ressourcen in ähnlicher Größenordnung benötigen,<br />

ist die Latenzzeit für die Festkomma-Lösung nur halb so<br />

lang. Ohne Folding besteht ein deutlich größerer Unterschied zwischen<br />

dem Gleitkomma- und dem Festkomma-Ansatz. Reduziert<br />

man die Genauigkeit auf 16 Bit, dann benötigt man aufgrund des<br />

schmaleren Datenpfades weniger Ressourcen.<br />

Fazit<br />

Da viele Entwickler nicht unbedingt vertraut mit FPGA- oder<br />

DSP-Applikationen sind, ist es wichtig Tools zur Verfügung zu<br />

stellen, die die Design-Produktivität erhöhen und die Entwicklungszeiten<br />

reduzieren. Dafür wurden von Altera Tools wie der<br />

SOPC Builder oder der DSP Builder entwickelt, mit denen Entwickler<br />

den konventionellen DSP-Entwicklungsprozess nutzen<br />

können und somit schnell zu der gewünschten Motorsteuerung<br />

kommen. (jj)<br />

n<br />

Der Autor: Stefano Zammattio ist Product Marketing Manager Altera Europe.<br />

Bilder: Altera<br />

www.<strong>elektronik</strong>-<strong>industrie</strong>.de <strong>elektronik</strong> <strong>industrie</strong> 07/2011 21<br />

18_Coverstory Altera_500 (.indd 21 30.06.2011 12:15:56