PDF-Ausgabe herunterladen (21.4 MB) - elektronik industrie

PDF-Ausgabe herunterladen (21.4 MB) - elektronik industrie

PDF-Ausgabe herunterladen (21.4 MB) - elektronik industrie

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Messtechnik<br />

PXI<br />

Bilder: National Instruments<br />

Multicore-CPUs für verteilte Verarbeitung<br />

Anwendungen aus den Bereichen SIGINT und echtzeitfähiges<br />

Hochleistungsrechnen, für die Daten inline oder in Echtzeit verarbeitet<br />

werden, müssen typischerweise über komplexe Datenverarbeitungsfunktionen<br />

verfügen, um den Datenfluss bewältigen zu<br />

können. Außerdem wird bei diesen Anwendungen die Verarbeitungslast<br />

mithilfe einer Kommunikationsschnittstelle, die eine hohe<br />

Bandbreite und geringe Latenz bietet, auf mehrere separate Verarbeitungsknoten<br />

verteilt. Für einige verteilte Verarbeitungssysteme<br />

reichen auch FPGAs und einzelne digitale Signalverarbeitungssysteme<br />

aus. Doch für bestimmte Anwendungen muss bestehendes<br />

x86-basiertes Software-IP genutzt werden oder die Berechnungen<br />

in Gleitkomma- statt in Festkommawerten angegeben werden. In<br />

solchen Fällen bietet PXImc die Möglichkeit, verteilte Verarbeitungssysteme<br />

zu erstellen, die die aktuellen, auf Multicore-CPU<br />

basierenden PCs als externe Rechenknoten nutzen. Dies bezieht<br />

sich nicht nur auf die zuvor aufgeführten Anforderungen, sondern<br />

bietet auch ein System mit kürzeren Entwicklungs- und Fehlerbehebungszeiten<br />

im Vergleich zu Systemen, die FPGA und benutzerdefinierte<br />

digitale Signalverarbeitungssysteme nutzen.<br />

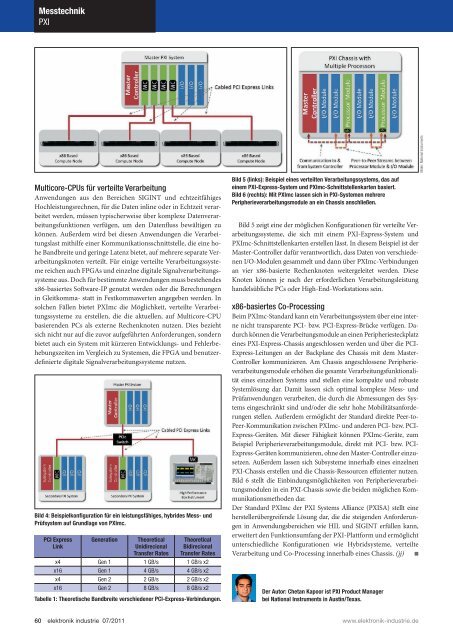

Bild 4: Beispielkonfiguration für ein leistungsfähiges, hybrides Mess- und<br />

Prüfsystem auf Grundlage von PXImc.<br />

PCI Express<br />

Link<br />

Generation<br />

Theoretical<br />

Unidirecional<br />

Transfer Rates<br />

Theoretical<br />

Bidirecional<br />

Transfer Rates<br />

x4 Gen 1 1 GB/s 1 GB/s x2<br />

x16 Gen 1 4 GB/s 4 GB/s x2<br />

x4 Gen 2 2 GB/s 2 GB/s x2<br />

x16 Gen 2 8 GB/s 8 GB/s x2<br />

Tabelle 1: Theoretische Bandbreite verschiedener PCI-Express-Verbindungen.<br />

Bild 5 (links): Beispiel eines verteilten Verarbeitungssystems, das auf<br />

einem PXI-Express-System und PXImc-Schnittstellenkarten basiert.<br />

Bild 6 (rechts): Mit PXImc lassen sich in PXI-Systemen mehrere<br />

Peripherieverarbeitungsmodule an ein Chassis anschließen.<br />

Bild 5 zeigt eine der möglichen Konfigurationen für verteilte Verarbeitungssysteme,<br />

die sich mit einem PXI-Express-System und<br />

PXImc-Schnittstellenkarten erstellen lässt. In diesem Beispiel ist der<br />

Master-Controller dafür verantwortlich, dass Daten von verschiedenen<br />

I/O-Modulen gesammelt und dann über PXImc-Verbindungen<br />

an vier x86-basierte Rechenknoten weitergeleitet werden. Diese<br />

Knoten können je nach der erforderlichen Verarbeitungsleistung<br />

handelsübliche PCs oder High-End-Workstations sein.<br />

x86-basiertes Co-Processing<br />

Beim PXImc-Standard kann ein Verarbeitungssystem über eine interne<br />

nicht transparente PCI- bzw. PCI-Express-Brücke verfügen. Dadurch<br />

können die Verarbeitungsmodule an einen Peripheriesteckplatz<br />

eines PXI-Express-Chassis angeschlossen werden und über die PCI-<br />

Express-Leitungen an der Backplane des Chassis mit dem Master-<br />

Controller kommunizieren. Am Chassis angeschlossene Peripherieverarbeitungsmodule<br />

erhöhen die gesamte Verarbeitungsfunktionalität<br />

eines einzelnen Systems und stellen eine kompakte und robuste<br />

Systemlösung dar. Damit lassen sich optimal komplexe Mess- und<br />

Prüfanwendungen verarbeiten, die durch die Abmessungen des Systems<br />

eingeschränkt sind und/oder die sehr hohe Mobilitätsanforderungen<br />

stellen. Außerdem ermöglicht der Standard direkte Peer-to-<br />

Peer-Kommunikation zwischen PXImc- und anderen PCI- bzw. PCI-<br />

Express-Geräten. Mit dieser Fähigkeit können PXImc-Geräte, zum<br />

Beispiel Peripherieverarbeitungsmodule, direkt mit PCI- bzw. PCI-<br />

Express-Geräten kommunizieren, ohne den Master-Controller einzusetzen.<br />

Außerdem lassen sich Subsysteme innerhalb eines einzelnen<br />

PXI-Chassis erstellen und die Chassis-Ressourcen effizienter nutzen.<br />

Bild 6 stellt die Einbindungsmöglichkeiten von Peripherieverarbeitungsmodulen<br />

in ein PXI-Chassis sowie die beiden möglichen Kommunikationsmethoden<br />

dar.<br />

Der Standard PXImc der PXI Systems Alliance (PXISA) stellt eine<br />

herstellerübergreifende Lösung dar, die die steigenden Anforderungen<br />

in Anwendungsbereichen wie HIL und SIGINT erfüllen kann,<br />

erweitert den Funktionsumfang der PXI-Plattform und ermöglicht<br />

unterschiedliche Konfigurationen wie Hybridsysteme, verteilte<br />

Verarbeitung und Co-Processing innerhalb eines Chassis. (jj) n<br />

Der Autor: Chetan Kapoor ist PXI Product Manager<br />

bei National Instruments in Austin/Texas.<br />

60 <strong>elektronik</strong> <strong>industrie</strong> 07/2011<br />

www.<strong>elektronik</strong>-<strong>industrie</strong>.de<br />

58_NI_502 (jj).indd 60 30.06.2011 13:25:14