Abschlussbericht

Abschlussbericht

Abschlussbericht

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

BSI, Bonn<br />

IHP, Frankfurt (Oder)<br />

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

Version 1.00<br />

13. Oktober 2011<br />

IHP: Prof. Dr. Peter Langendörfer / Frank Vater / Thomas Basmer / Oliver Stecklina<br />

BSI: Frank Gehring, Christian Wieschebrink

2<br />

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node

Inhaltsverzeichnis<br />

1 Einleitung 13<br />

1.1 Beschreibung des Gesamtsystems . . . . . . . . . . . . . . . . . . . . . . . 14<br />

2 Hardware 15<br />

2.1 Beschreibung der Teilkomponenten . . . . . . . . . . . . . . . . . . . . . . . 15<br />

2.2 LEON2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15<br />

2.3 AMBA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16<br />

2.4 Konfigurationsregister . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18<br />

2.5 Memory-Controller und Integration der Hardwarebeschleuniger . . . . . . . 18<br />

2.6 Speicher . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19<br />

2.7 Parallel I/O-Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20<br />

2.8 UART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20<br />

2.9 DSU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

2.10 Interrupt-Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

2.11 Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

2.12 Memory-Like Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

2.13 AES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22<br />

2.13.1 Arithmetische Grundlagen . . . . . . . . . . . . . . . . . . . . . . . . 23<br />

2.13.2 Algorithmusbeschreibung des AES . . . . . . . . . . . . . . . . . . . 24<br />

2.13.3 Implementierung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26<br />

2.14 ECC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26<br />

2.14.1 Arithmetische Grundlagen . . . . . . . . . . . . . . . . . . . . . . . . 27<br />

2.14.2 Multiplizierer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28<br />

2.14.3 Reduktion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28<br />

2.14.4 System-Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29<br />

2.14.5 Parameter im TSN . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31<br />

2.15 SHA-1 / PRNG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32<br />

2.15.1 Secure Hash Algorithmus . . . . . . . . . . . . . . . . . . . . . . . . 33<br />

2.15.2 Pseudo Random Number Generator (PRNG) . . . . . . . . . . . . . 36<br />

2.15.3 Hardwarebeschreibung . . . . . . . . . . . . . . . . . . . . . . . . . 37<br />

2.16 SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39<br />

2.17 Pads und Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39<br />

2.18 Vom VHDL zum ASIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40<br />

2.19 Layoutgenerierung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41<br />

2.20 Boardbeschreibung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42<br />

2.21 Systemtest und Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42<br />

2.22 Energie . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43<br />

2.23 Debug- und Diagnoseschnittstellen . . . . . . . . . . . . . . . . . . . . . . . 44

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

3 Software 45<br />

3.1 Das Betriebssystem eCos . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45<br />

3.1.1 eCos im Detail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45<br />

3.1.2 Hinzufügen von Komponenten . . . . . . . . . . . . . . . . . . . . . 48<br />

3.1.3 build-Prozess . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51<br />

4 Softwarearchitektur des TSN 57<br />

4.1 Gerätetreiber . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58<br />

4.1.1 UART Treiber . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58<br />

4.1.2 SPI Treiber . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59<br />

4.1.3 MMIO Treiber . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60<br />

4.1.4 General Purpose Input/Output (GPIO) Treiber . . . . . . . . . . . . . 61<br />

4.2 Services . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62<br />

4.2.1 CryptAPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62<br />

4.2.2 SensorAPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64<br />

4.3 Protokollstapel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64<br />

4.3.1 lightweight IP Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . 65<br />

4.3.2 Point to Point Protocol (PPP) . . . . . . . . . . . . . . . . . . . . . . 66<br />

4.3.3 Bluetooth Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66<br />

4.3.4 Sensor Protokoll . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68<br />

4.4 TSN Threads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69<br />

4.4.1 Bridge Thread . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69<br />

4.4.2 Schlüsselaustausch Thread . . . . . . . . . . . . . . . . . . . . . . . 70<br />

4.4.3 Sensorik Thread . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70<br />

4.4.4 Management Thread . . . . . . . . . . . . . . . . . . . . . . . . . . . 70<br />

5 Simulation und Messergebnisse 73<br />

5.1 Ziel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73<br />

5.2 Messaufbau . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73<br />

5.3 Messprogramm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74<br />

5.4 Messungen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75<br />

5.5 Lebensdauertest . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76<br />

6 Future Work 77<br />

6.1 System-Architektur . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77<br />

6.1.1 Mikrokern-basierter TSN mit Security Compartments . . . . . . . . . 78<br />

6.1.2 Trusted Computing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82<br />

6.1.3 TCP/IP Netzwerk-Stack . . . . . . . . . . . . . . . . . . . . . . . . . 90<br />

6.2 Optimiertes Hardwarekonzept . . . . . . . . . . . . . . . . . . . . . . . . . . 95<br />

6.2.1 Einfügen neuer Komponenten . . . . . . . . . . . . . . . . . . . . . 96<br />

6.2.2 Veränderungen an vorhandenen Komponenten . . . . . . . . . . . . 100<br />

6.2.3 Schutzkonzept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105<br />

6.3 Energieversorgung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112<br />

6.3.1 Einführung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112<br />

6.3.2 Boardkomponenten . . . . . . . . . . . . . . . . . . . . . . . . . . . 112<br />

6.3.3 Alternativen zur Energieversorgung aus Primärbatterien . . . . . . . 112<br />

Abkürzungsverzeichnis 115<br />

4

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

Literaturverzeichnis 117<br />

5

Tabellenverzeichnis<br />

1.1 Eigenschaften des TSN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14<br />

2.1 Signale eines Memory-Like Interface . . . . . . . . . . . . . . . . . . . . . . 22<br />

2.2 Struktur des Kontrollregisters . . . . . . . . . . . . . . . . . . . . . . . . . . 38<br />

2.3 Adressen der SHA-1-Register . . . . . . . . . . . . . . . . . . . . . . . . . . 39<br />

2.4 Simulation der Leistungsaufnahme für Einzelkomponenten und das Gesamtsystem<br />

bei 16 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44<br />

3.1 Speichergrößen verschiedener Konfigurationen von eCos 3.0 . . . . . . . . 45<br />

4.1 Konfigurationskommandos des MMIO Treibers . . . . . . . . . . . . . . . . 61<br />

4.2 AT-Kommandos des Bluebear SP-S . . . . . . . . . . . . . . . . . . . . . . 68<br />

5.1 Messungen der Stromaufnahme für den AES . . . . . . . . . . . . . . . . . 76<br />

5.2 Messungen der Stromaufnahme für den ECC . . . . . . . . . . . . . . . . . 76<br />

6.1 Vergleich verschiedener Multiplizierer für Punktmultiplikation der ECC Komponente<br />

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Abbildungsverzeichnis<br />

1.1 Anwendungsbeispiel des TSN . . . . . . . . . . . . . . . . . . . . . . . . . 13<br />

2.1 Blockschaltbild des TSN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15<br />

2.2 Grafische Darstellung der fünfstufigen Pipeline des LEON2 (entnommen<br />

aus LEON2 Processor User’s Manual) [3] . . . . . . . . . . . . . . . . . . . 17<br />

2.3 Aufbau des AMBA-Bus-Systems im TSN . . . . . . . . . . . . . . . . . . . . 17<br />

2.4 Verwendung eines AES-Blocks mit einem memory-like Interface . . . . . . 19<br />

2.5 Schlüsseladdition für 128 Bit . . . . . . . . . . . . . . . . . . . . . . . . . . 24<br />

2.6 Schematischer Aufbau der AES-Implementierung . . . . . . . . . . . . . . . 24<br />

2.7 Spaltenweise Generierung des nächsten Rundenschlüssels . . . . . . . . . 26<br />

2.8 Da das Ergebnis einer Multiplikation länger als die maximale Feldlänge ist,<br />

benötigt man einen Reduktionsschritt, der das Ergebnis innerhalb des Feldes<br />

reduziert. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29<br />

2.9 Blockschaltbild des 233-Bit-ECC-Beschleunigers. Ein 233 Bit breiter, von<br />

einer Controller-Einheit kontrollierter Bus verbindet die Rechen- und Registereinheiten.<br />

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31<br />

2.10 Resultate der verschiedenen ECC-Beschleuniger-Schaltungen. Die Balken<br />

zeigen die benutzte Siliziumfläche. Die Linien entsprechen dem Energieverbrauch.<br />

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31<br />

2.11 Ablauf der Signatur mit Hilfe von Soft- und Hardware . . . . . . . . . . . . . 33<br />

2.12 Blockschaltbild des SHA-1-Moduls . . . . . . . . . . . . . . . . . . . . . . . 37<br />

2.13 Gehäuse des TSN vom Typ QFP128 . . . . . . . . . . . . . . . . . . . . . . 40<br />

2.14 Test eines entwickelten Hardware-Modells . . . . . . . . . . . . . . . . . . . 41<br />

2.15 Layout des TSN-Chip nach der Verdrahtung. Insbesondere die Verdrahtung<br />

auf den beiden obersten Metallebenen (hier: gelb und braun) treten hervor 41<br />

2.16 Analyse der Leistungsaufnahme des Gesamtsystems (rot) sowie selektierter<br />

Einzelkomponenten. Der grüne Plot zeigt exemplarisch den deutlich erhöhten<br />

Stromverbrauch des ECC-Beschleunigers in seiner Aktivitätsphase. 43<br />

3.1 eCos-Systemarchitektur . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47<br />

4.1 Softwarearchitektur des TSN . . . . . . . . . . . . . . . . . . . . . . . . . . 57<br />

4.2 SPI Chip Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60<br />

4.3 Die Protokollstapel des TSN . . . . . . . . . . . . . . . . . . . . . . . . . . . 65<br />

4.4 Zustandsautomat der Sensorüberwachung . . . . . . . . . . . . . . . . . . 71<br />

4.5 Management der TSN Threads . . . . . . . . . . . . . . . . . . . . . . . . . 71<br />

6.1 Auswirkung von Fehlern in Betriebssystemen ohne Security Compartments 79<br />

6.2 Schutz von Betriebssystemkomponenten durch Security Compartments . . 79

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

6.3 Aufteilung von Diensten und Services in monolithischen und µKern-Betriebssystemen<br />

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81<br />

6.4 Integration des Sicherheitsmoduls in den Trusted Sensor Node (TSN) . . . 83<br />

6.5 Trusted Boot eines L4-basierten Systems mit Signatur-basierter Modulauthentifizierung<br />

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85<br />

6.6 Kryptographisch gesichertes Programmcode Update . . . . . . . . . . . . . 87<br />

6.7 Kategorisierung der Ansätze zur Verbesserung der TCP-Performanz in heterogenen<br />

Netzwerken . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94<br />

6.8 Anzahl der in den drahtlosen Kanal gesendeten Bytes in Abhängigkeit von<br />

der Anzahl der Übertragungswiederholungen im Medium Access Control<br />

(MAC) und der Bitfehlerrate (BER) . . . . . . . . . . . . . . . . . . . . . . . 95<br />

6.9 Datenrate in Abhängigkeit von der Paketgröße auf MAC bzw. Transmission<br />

Control Protocol (TCP) Ebene, und der Bitfehlerrate (BER) . . . . . . . . . 96<br />

6.10 Clockgating-Controller bestehend aus Latch und OR-Gatter . . . . . . . . . 97<br />

6.11 Finite-State-Machine mit 5 Zuständen . . . . . . . . . . . . . . . . . . . . . 98<br />

6.12 Zunahme der Leckströme bei Verkleinerung der Strukturgröße[1] . . . . . . 98<br />

6.13 Darstellung eines Power-Gating-Controllers . . . . . . . . . . . . . . . . . . 99<br />

6.14 Darstellung einer Power-Gating Architektur . . . . . . . . . . . . . . . . . . 99<br />

6.15 Veränderte Anbindung der kryptografischen Komponenten zwischen Memory-<br />

Controller und Speicher . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100<br />

6.16 BGA-Gehäuse (Unterseite) . . . . . . . . . . . . . . . . . . . . . . . . . . . 105<br />

6.17 TSN in einem offenen PQFP-128-Gehäuse . . . . . . . . . . . . . . . . . . 106<br />

6.18 Trägerplatine mit aufgebondeten ASICs . . . . . . . . . . . . . . . . . . . . 107<br />

6.19 Chip in einem BGA-Gehäuse . . . . . . . . . . . . . . . . . . . . . . . . . . 107<br />

6.20 Trägerplatine mit teilweise vergossenen Kondensatoren . . . . . . . . . . . 108<br />

6.21 Anbindung der Authentifizierungskomponente in den TSN . . . . . . . . . . 108<br />

6.22 Authentifizierung des Nutzers am TSN, um Man-In-The-Middle Attacken zu<br />

vermeiden . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109<br />

6.23 Authentifizierung zwischen Nutzer und TSN zum Start einer neuen Session<br />

mit Schutz Replay-Attacken . . . . . . . . . . . . . . . . . . . . . . . . . . . 110<br />

10

Listings<br />

2.1 Beispielcode zum Ansprechen des AES am Memory-Controller . . . . . . . 22<br />

2.2 Unterfunktionen f und K . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34<br />

2.3 Der Algorithmus von G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35<br />

3.1 Package–Verzeichnisbaum . . . . . . . . . . . . . . . . . . . . . . . . . . . 49<br />

3.2 Package–Defintion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49<br />

3.3 Package–Registration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50<br />

3.4 Device Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51<br />

3.5 Device IO Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51<br />

3.6 Application Skeleton . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55<br />

5.1 Code für maximalen Datendurchsatz des AES . . . . . . . . . . . . . . . . 74<br />

6.1 Schreibbefehl für die Verschlüsselung von Daten mit expliziten Adressen . 101<br />

6.2 Schreibbefehl für die Verschlüsselung von Daten auf eine Adresse . . . . . 101

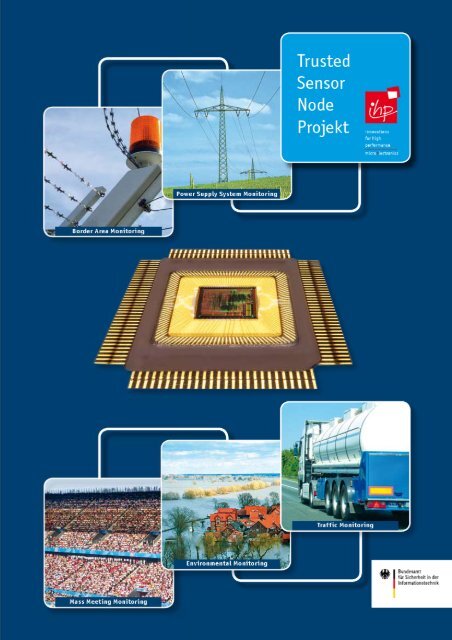

1 Einleitung<br />

Drahtlose Sensornetze werden heute in vielen Bereichen, wie zum Beispiel der Industrieautomatisierung,<br />

Umweltdatenerfassung und Überwachung von Infrastrukturen eingesetzt.<br />

Aus Gründen des Schutzes vor Ausspähung von Betriebsgeheimnissen, Manipulation und<br />

Sabotage von Anlagen, zum Beispiel im Bereich der biologischen und chemischen Prozesstechnologie,<br />

aber auch im Bereich der Homeland Security, werden hohe Sicherheitsanforderungen<br />

an drahtlose Sensorknoten gestellt. Insbesondere die Verwendung des Mediums<br />

Luft macht diese Geräte leicht angreifbar, da kein physikalischer Zugang für das<br />

Abhören oder die Manipulation der Daten und Geräte benötigt wird. Dem Einsatz starker<br />

kryptographischer Mechanismen stehen jedoch im Regelfall die begrenzten Ressourcen<br />

der drahtlosen Sensorknoten entgegen.<br />

Im Rahmen des Projekts „Trusted Sensor Node“ (TSN) sollte ein vertrauenswürdiger Sensorknoten<br />

für das Bundesamt für Sicherheit in der Informationstechnik (BSI) entwickelt<br />

werden. Dieser Knoten fungiert als Bridge zwischen „einfachen“ Sensorknoten, die der<br />

Detektion von Ereignissen dienen, und einer Datensenke. Für die Kommunikation im Sensornetzwerk<br />

wird IEEE 802.15.4 eingesetzt. Die Kommunikation mit der Datensenke erfolgt<br />

auf Basis der Bluetooth-Technologie. Dieser TSN soll zudem die erste vertrauenswürdige<br />

Instanz in der Netzwerktopologie bilden. Deshalb wurde eine Unterstützung starker kryptographischer<br />

Verfahren durch entsprechende Hardwarebeschleuniger vorgesehen.<br />

IEEE 802.15.4<br />

iSense<br />

iSense<br />

IEEE 802.15.1<br />

TSN<br />

iSense<br />

Basestation<br />

iSense<br />

iSense<br />

Abbildung 1.1: Anwendungsbeispiel des TSN

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

1.1 Beschreibung des Gesamtsystems<br />

Der TSN-Knoten setzt sich zusammen aus einem Singlechip, welcher aus einem Prozessor<br />

und den Hardwarebeschleunigern besteht und den externen Komponenten wie Funkmodulen<br />

und zusätzlichem Speicher, die auf dem Board mit dem Core kombiniert werden.<br />

Der Knoten fungiert als Bridge zwischen Bluetooth und IEEE 802.15.4 (siehe Abbildung<br />

1.1). Um dies zu ermöglichen, muss der TSN mit zwei unterschiedlichen externen Radiomodulen<br />

ausgestattet sein. Neben diesen Funkmodulen müssen auch Sensoren und<br />

zusätzliche Speicher (RAM, Flash) an den TSN angeschlossen werden. Die notwendigen<br />

Schnittstellen sind in den TSN integriert. Das Blockschaltbild in Abbildung 2.1 verdeutlicht<br />

den Aufbau des Sensorknotens.<br />

Um die Sicherheitsanforderungen erfüllen zu können wurde der TSN abweichend vom<br />

LEON2-Referenz-Design [1] um Co-Prozessoren für AES, SHA-1/PRNG sowie ECC erweitert.<br />

Sie werden zum Ver- und Entschlüsseln von Daten sowie zur Signierung von<br />

Nachrichten eingesetzt. Die Zusatzmodule dienen somit einer sicheren Verarbeitung und<br />

Übertragung von Daten.<br />

Für die Anbindung externer Sensoren steht der Serial Peripheral Interface (SPI)-Master zur<br />

Verfügung. An diesen können bis zu drei SPI-Slave-Komponenten angeschlossen werden.<br />

Die vorgesehenen Radiomodule werden über zwei UART-Schnittstellen mit dem System<br />

verbunden. Der externe Speicher wird direkt an den Memory Controller angeschlossen.<br />

Tabelle 1.1 zeigt die Systemeigenschaften des TSN-ASICs. Er wird mit der IHP-eigenen<br />

0,25-µm-Technologie gefertigt.<br />

Fläche 30mm 2<br />

Signalpins 87<br />

Powerpins 24<br />

BIST/Scan-Ports 5<br />

Cache<br />

2x4kByte<br />

Maximale Taktfrequenz 16 MHz<br />

Corespannung 2,5 V<br />

Padspannung<br />

3,3 V<br />

Tabelle 1.1: Eigenschaften des TSN<br />

14

2 Hardware<br />

2.1 Beschreibung der Teilkomponenten<br />

Wie im Blockschaltbild (siehe Abbildung 2.1) zu erkennen ist, setzt sich der TSN aus verschiedenen<br />

Hardwarekomponenten zusammen. Diese werden in diesem Kapitel genauer<br />

erläutert.<br />

Programming<br />

Interface<br />

Sensors<br />

802.15.4<br />

Module<br />

D-Cache<br />

I-Cache<br />

Scanchain<br />

DSU<br />

SPI<br />

(Master)<br />

UART<br />

Bluetooth<br />

Module<br />

LEON2<br />

Processor<br />

Core<br />

AMBA AHB<br />

Bridge<br />

(Master)<br />

AMBA APB<br />

Memory Controller<br />

Intr<br />

Ctrl<br />

Timer<br />

GPIO<br />

Sensors<br />

AES<br />

ECC<br />

SHA1<br />

PRNG<br />

Flash<br />

RAM<br />

Abbildung 2.1: Blockschaltbild des TSN<br />

2.2 LEON2<br />

Das Herz des TSN bildet der LEON2, ein 32-Bit-RISC-Prozessor. Der Chip ist als VHDL-<br />

Modell von Gaisler Research [2] entwickelt worden und steht als „Open Source“-Komponente<br />

unter der Lesser GNU Public License (LGPL) [31] zur Verfügung.<br />

Als Grundlage dient die SPARC-V8-Architektur, die in IEEE 1754 beschrieben ist. Der Chip<br />

enthält separate Befehls- und Datencaches, Interrupt-Controller, Timer, Debug-Unterstüt-

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

zung und ein einfaches Powermanagement. Als zentrales Bussystem dient der AMBA-Bus<br />

[4], über den auch zusätzliche Peripherie angeschlossen werden kann.<br />

Der LEON2 besitzt eine fünfstufige Pipeline für die Befehlsverarbeitung (siehe Abbildung<br />

2.2) und in der vorliegenden Konfiguration einen Satz von 8 Register-Windows. Die Instruktions-Pipeline<br />

ist folgendermaßen aufgebaut:<br />

• Stufe 1: Instruktion holen (Fetch)<br />

Instruktion aus dem Instruktionscache oder über den Memory-Controller aus dem<br />

Speicher holen.<br />

• Stufe 2: Instruktion dekodieren (Decode)<br />

Instruktion wird dekodiert und die Operanden werden aus dem entsprechenden Register-Window<br />

gelesen.<br />

• Stufe 3: Instruktion ausführen (Execute)<br />

Operation der Arithmetisch-Logischen Einheit wird ausgeführt.<br />

• Stufe 4: Speicherzugriff (Memory)<br />

Ergebnisse aus der Stufe 3 werden in den Datencache zurückgeschrieben.<br />

• Stufe 5: Schreiben (Write)<br />

Ergebnisse der Operationen aus Stufe 3 werden in entsprechende Register-Windows<br />

zurückgeschrieben.<br />

Unter der Voraussetzung, dass sich die nötigen Daten im Cache befinden, wird ein Großteil<br />

der Instruktionen in einem Clockzyklus abgearbeitet. Ausgenommen hiervon sind die<br />

Jump-, Load- und Store-Operationen.<br />

In der Konfiguration des LEON2 besteht die Möglichkeit, einen Hardwaremultiplizierer in<br />

das Design zu integrieren. Dadurch werden die Multiplikationsoperationen beschleunigt.<br />

Die hierdurch beschleunigten Operationen würden, falls überhaupt, als Teil der kryptographischen<br />

Operationen benötigt. Da für diese bereits Hardwarebeschleuniger vorgesehen<br />

sind, wurde zur Minimierung der Chipfläche auf die Integration eines solchen Multiplizierers<br />

verzichtet.<br />

2.3 AMBA<br />

Der Advanced Microcontroller Bus Architecture (AMBA)-Bus wird zur Kommunikation der<br />

Komponenten auf einem Application Specific Integrated Circuit (ASIC) verwendet [4]. Er<br />

besteht in der Regel aus zwei Untersystemen, dem Advanced High-performance Bus<br />

(AHB) und dem Advanced Peripheral Bus (APB).<br />

Der AHB wird verwendet, um Komponenten mit hohen Datentransferraten zu verbinden.<br />

Prozessor, Speicher sowie gegebenenfalls Co-Prozessoren sind über diesen schnellen<br />

Datenbus angebunden.<br />

16

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

Abbildung 2.2: Grafische Darstellung der fünfstufigen Pipeline des LEON2<br />

(entnommen aus LEON2 Processor User’s Manual) [3]<br />

Der APB hingegen ist auf Energieeffizienz optimiert und besonders geeignet, langsame<br />

Peripherie, wie z.B. serielle Schnittstellen, in das System zu integrieren. Der AHB und der<br />

APB sind über eine Bridge miteinander verbunden. Durch das Hinzufügen des APB bleibt<br />

die hohe Leistungsfähigkeit des AMBA-Busses auch im Fall des Zugriffs auf langsame<br />

Komponenten erhalten.<br />

Der AHB im TSN (siehe Abbildung 2.3) enthält einen AHB-Master mit dem LEON2-Prozessor<br />

und zwei AHB-Slaves, den Memory-Controller sowie die APB-Bridge. Ein AHB-Master<br />

kann einen Zugriff auf den AHB initialisieren, während ein AHB-Slave nur auf Transaktionen<br />

(Lese- oder Schreibbefehl) reagieren kann.<br />

Prozessor mit<br />

Pipeline<br />

D-Cache I-Cache<br />

AHB-Master<br />

AHB<br />

AHB/APB-Bridge<br />

(AHB-Slave)<br />

Memory-Controller<br />

(AHB-Slave)<br />

UART<br />

SPI<br />

Abbildung 2.3: Aufbau des AMBA-Bus-Systems im TSN<br />

17

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

2.4 Konfigurationsregister<br />

Am APB sind die Konfigurations- und teilweise auch die Datenregister der Komponenten<br />

angeschlossen. Dazu gehören die Register für den Memory-Controller, für UART, SPI,<br />

PIO, Timer und den Interrupt-Controller.<br />

2.5 Memory-Controller und Integration der<br />

Hardwarebeschleuniger<br />

Der Memory-Controller übernimmt die wesentliche Aufgabe, alle Zugriffe auf die Speicherelemente<br />

zu koordinieren und durchzuführen. Das umfasst als Speicher- und speicherähnliche<br />

Elemente den Flash, den memory-mapped I/O sowie den SRAM.<br />

Unter „memory-mapped I/O“ versteht man den Zugriff auf Blöcke, die zwar ein Interface<br />

wie ein Speicher besitzen, dessen Funktionalität jedoch eine andere ist (z.B. Co-Prozessor<br />

zur Datenverarbeitung). Der I/O-Bereich wird so in den Arbeitsspeicher eingeblendet.<br />

Man kann ein neues Hardwaremodul mit einem proprietären Interface ausstatten, das von<br />

der jeweiligen Funktion der Hardwarekomponente bestimmt wird. Für den AES könnte<br />

das zum Beispiel bedeuten, dass die Schnittstelle einen Eingang für Clock und Reset<br />

sowie Eingänge mit einer Breite von 128 Bit für die Daten und weiteren 128 Bit für den<br />

Schlüssel hat. Der Ausgang für die Daten wäre ebenso 128 Bit breit. Dieses, zunächst<br />

nahe liegende, Interface ist jedoch nicht brauchbar, da es keine passende Hardware gibt,<br />

an die die Komponente angeschlossen werden kann.<br />

Es muss also ein etwas höherer Aufwand betrieben werden, um die neue Komponente mit<br />

der gleichen Schnittstelle wie von Speicherblöcken auszustatten. Diese Art der Schnittstelle<br />

wird „memory-like Interface“ genannt. Durch das vergleichsweise einfach ausgeführte<br />

Interface eines Speichers (Clock, Daten- und Adressbus, Read- und Write-Enable) ist<br />

diese Art der Anbindung weit verbreitet. Daher wurde für den AES, SHA-1 und den ECC<br />

ein solches Interface gewählt (siehe Abbildung 2.4). Prinzipiell ließen sich die Komponenten<br />

auch als SRAM anschließen. Das hat jedoch den Nachteil, dass dieser „cacheable“<br />

ist und somit oftmals bei Lesevorgängen auf den Cache zugegriffen wird anstelle eines<br />

direkten Lesezugriffs. Der Cache enthält an dieser Stelle jedoch veraltete Daten, da der<br />

Co-Prozessor die Daten modifiziert hat. So werden falsche Ergebnisse zurück geliefert.<br />

Mit der Verwendung von memory-mapped I/O wird das Problem vollständig umgangen.<br />

In der Ausgangskonfiguration erlaubt der LEON2 die Anbindung einer Komponente an<br />

den memory-mapped I/O. Dieses ist für den TSN nicht ausreichen, da AES, ECC und<br />

SHA-1 angeschlossen werden muss. Durch die Aufteilung des Adressbereich für memorymapped<br />

I/O in drei Unterbereiche wird der Anschluß aller Komponenten ermöglicht.<br />

Während memory-mapped I/O den nicht gepufferten Zugriff mittels Memory-Controller auf<br />

die Komponente meint, ist das memory-like Interface die Beschreibung der Schnittstelle.<br />

18

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

Zu Konfigurationszwecken besitzt der Memory-Controller drei Konfigurationsregister. Mit<br />

dessen Hilfe werden die Wortbreite (8, 16 oder 32 Bit), Zugriffszeiten sowie Speichergrößen<br />

definiert. Alle Signale liegen jederzeit an den angeschlossenen Komponenten an. Einzige<br />

Ausnahme bildet hierbei das „Chip-Select“-Signal, welches exklusiv für jede Komponente<br />

ist. Anhand dieses Signals erkennt das Modul, ob es angesprochen wird. Unabhängig<br />

vom Memory-Controller agiert der Cache, welcher direkt mit dem Prozessor verbunden<br />

ist.<br />

CHIP_SELECT<br />

CLOCK<br />

Memory-Controller<br />

RESET<br />

WRITE<br />

RAM<br />

DATA_OUT<br />

ADDR<br />

DATA_IN<br />

AMBA-Bus<br />

AES<br />

DATA_OUT<br />

LEON2<br />

CHIP_SELECT<br />

Abbildung 2.4: Verwendung eines AES-Blocks mit einem memory-like Interface<br />

2.6 Speicher<br />

Der TSN verfügt über verschiedenartige Speicher. Der 4-KByte-Befehlscache und der 4-<br />

KByte-Datencache beschleunigen das System durch ihre direkte Anbindung an den Prozessor.<br />

Der TSN ist mit RAM ausgestattet, der auf dem Board untergebracht ist. Dessen<br />

Größe ist variabel zwischen 16 Kilobyte und 16 Megabyte. Derzeit ist das Board mit einem<br />

2-Megabyte-Modul bestückt.<br />

Der RAM ist über den Memory-Controller mit einer Wortbreite von 32 Bit an den schnellen<br />

AMBA-AHB-Bus angeschlossen. Zur Minimierung der Chipfläche wurde nur der Cache in<br />

den Chip integriert. Durch die Art der Ausführung des Memory-Controllers ist sichergestellt,<br />

dass der Zugriff auf den externen RAM genauso schnell ist, wie auf dem internen<br />

RAM. Aufgrund der beschränkten Anzahl an I/O-Pins (siehe Abschnitt 2.17) kann der externe<br />

Speicher nur mit 16 Bit Wortbreite angesprochen werden, so dass für das Schreiben<br />

und Lesen eines 32-Bit-Wortes jeweils zwei Zugriffe stattfinden müssen. Durch die Verwendung<br />

von Cache wird der Geschwindigkeitsnachteil im laufenden Betrieb so weit wie<br />

möglich kompensiert werden.<br />

Ein sicherer Speicher ist in der vorliegenden Entwicklungsstufe nicht das Entwurfsziel, da<br />

zunächst die Gesamtarchitektur des Systems geprüft werden soll. Um in späteren Entwicklungsstadien<br />

einen sicheren Speicher zu realisieren, genügt es nicht, den Speicher<br />

vollständig on-Chip auszuführen. Er wird vielmehr dadurch erreicht, dass alle Daten verschlüsselt<br />

abgelegt werden. Dies ist notwendig, um eine Abfrage des internen Speichers<br />

19

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

durch physikalische Angriffe zu verhindern. RAM-Strukturen sind besonders problematisch,<br />

da die Speicherelemente in einem gefertigten Design sehr gut zu identifizieren und,<br />

mit der richtigen Technik auch auslesbar sind.<br />

Eine Komponente zur Ansteuerung eines sicheren Speichers ermöglicht es auch, externen<br />

Speicher „sicher“ anzuschließen und lässt somit genügend Spielraum für die Speichererweiterung.<br />

2.7 Parallel I/O-Port<br />

Der Parallel I/O-Port ist ein bitweise programmierbarer I/O-Port (PIO). In der Basiskonfiguration<br />

des LEON2 werden alle 32 Bit nach außen geführt. Dabei werden die Pins für die<br />

Ports 0 bis 15 mit den UART-Ports sowie Konfigurationspins für den Bootvorgang geteilt<br />

um Pins einzusparen. Über ein Konfigurationsregister wird die jeweils gewünschte Funktion<br />

ausgewählt, also als Eingang oder Ausgang. Für den Fall, dass der Pin als Eingang<br />

agiert, kann der Wert, der am Pin von außen anliegt, über ein Register abgefragt werden.<br />

Ist der Pin als Ausgang konfiguriert, so muss der Wert am Ausgang gesetzt werden<br />

(logisch „0“ oder „1“).<br />

Durch das mögliche bitweise Ansprechen der Datenpins ist es auch möglich, Kommunikationsprotokolle<br />

in Software nachzubilden. Zum Beispiel sieht die aktuelle Umsetzung des<br />

TSN kein Modul für die I 2 C-Schnittstelle vor. Sollte sich die Notwendigkeit einer solchen<br />

ergeben, wird diese in Software, zu Lasten der gesamten Systemperformance, abgearbeitet.<br />

2.8 UART<br />

Die beiden Universal Asynchronous Receiver Transmitter (UART)-Komponenten sind Bestandteil<br />

des LEON2-Prozessors. Um Pins am Prozessor zu sparen, teilen sich die UARTs<br />

ihre Anschlüsse mit einigen PIO-Pins.<br />

Für die Datenübertragung muss der UART, der direkt an den APB angeschlossen ist, konfiguriert<br />

werden. Dabei können der UART-Takt, die Übertragungsrichtung und zahlreiche<br />

Sicherungsmechanismen eingestellt werden. Um Daten übertragen zu können, müssen<br />

diese in die entsprechenden Register geschrieben werden.<br />

Getestet wurden die UART-Schnittstellen, indem beide miteinander verbunden wurden.<br />

Abwechselnd wurden sie als Sender und Empfänger konfiguriert und Datenübertragungen<br />

initiiert.<br />

20

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

2.9 DSU<br />

Die Debug Support Unit (DSU) unterstützt die Fehlersuche und den Test des Systems.<br />

Sie ist integraler Bestandteil des LEON2-Prozessors und mit dem AMBA-AHB verbunden.<br />

Dies ermöglicht, den TSN in einen Debugmodus zu versetzen. Dabei wird der Prozessor<br />

angehalten, um Daten an jeder beliebigen Adresse lesen und schreiben zu können.<br />

2.10 Interrupt-Controller<br />

Der Interrupt-Controller dient als zentrale Instanz zur Signalisierung von Ausnahmezuständen.<br />

Ein Ausnahmezustand kann z. B. sein, dass in einem UART-Block Daten zur Abholung<br />

bereitstehen. Solange die CPU diese Daten nicht ausgelesen hat, können keine weiteren<br />

Daten empfangen werden. Daher ist es notwendig, die CPU über den Erhalt dieser Daten<br />

zu informieren und eine zügige Abarbeitung zu forcieren. Diese erfolgt durch das Auslösen<br />

eines Interrupts. Mittels des Interrupt-Controllers kann die CPU auswerten, welche<br />

Komponente den Interrupt ausgelöst hat und wie der Ausnahmezustand zu behandeln ist.<br />

2.11 Timer<br />

Die Timerkomponente besteht aus einem Prescaler und zwei Timern. Der Prescaler dient<br />

dazu, den Takt der Systemclock zu reduzieren. Die Timer dekrementieren einen vorher<br />

festgelegten Wert. Erreicht ein Timer den Wert „Null“, so wird mit Hilfe des Interrupt-<br />

Controllers ein Interrupt ausgelöst, den der Prozessor entsprechend beantworten muss.<br />

Dafür setzt der Prozessor zunächst den Interrupt zurück und signalisiert, dass der Interrupt<br />

bearbeitet wird. Anschließend wird eine vom Programmierer vorgegebene Softwareroutine<br />

abgearbeitet.<br />

2.12 Memory-Like Interface<br />

Die Schnittstellen des Advanced Encryption Standard (AES), Elliptic Curve Cryptography<br />

(ECC) und Secure Hash Algorithmus 1 (SHA-1) sind so ausgelegt, dass sie an den<br />

Memory-Controller angeschlossen werden können (siehe Tabelle 2.1).<br />

Das Listing 2.1 zeigt einen Beispielcode wie ein AES mit einem memory-like Interface<br />

in Software angesprochen wird. Die Funktion „writeReg“ hat als erstes Argument den zu<br />

schreibenden Wert und als zweites die Zieladresse. Es werden keine gesonderte Compilerbefehle<br />

benötigt, so dass auch keine Veränderungen am Compiler vorgenommen werden<br />

müssen.<br />

21

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

RESETN<br />

CLK<br />

CE<br />

OEN<br />

WE<br />

A [15 ... 0]<br />

d_in[31 ... 0]<br />

d_out[31 ... 0]<br />

ist ein low-aktiver Eingang. Es setzt das Modul zurück, in dem es die<br />

Register mit dem Startwert „0“ belegt. Die State-Machine geht in den<br />

Startzustand.<br />

ist der Eingang für das externe Taktsignal.<br />

ist ein low-aktiver Eingang. Er selektiert und aktiviert die Komponente.<br />

ist ein low-aktiver Eingang. Er wird während eines Lesezyklus auf aktiv<br />

gesetzt.<br />

ist der low-aktive Eingang, der einen Schreibzugriff signalisiert.<br />

ist der Adressbus. Dieser Eingang beinhaltet die Adressen der verschiedenen<br />

Register.<br />

ist ein 32 Bit Dateneingang. Er enthält die Daten, die in die adressierten<br />

Register geschrieben werden sollen.<br />

ist ein Datenausgang, der die Daten beinhaltet, die aus den Registern<br />

gelesen werden.<br />

Tabelle 2.1: Signale eines Memory-Like Interface<br />

// AES base address<br />

#define AESBASE 0x20200000 //memory mapped IO<br />

//Write key<br />

writeReg(0x2b7e1516, AESBASE + KEYBASE + 0);<br />

writeReg(0x28aed2a6, AESBASE + KEYBASE + 1);<br />

writeReg(0xabf71588, AESBASE + KEYBASE + 2);<br />

writeReg(0x09cf4f3c, AESBASE + KEYBASE + 3);<br />

writeReg(0x3243f6a8, AESBASE + DATABASE + ENCRYPTION + 0);<br />

writeReg(0x885a308d, AESBASE + DATABASE + ENCRYPTION + 0);<br />

writeReg(0x313198a2, AESBASE + DATABASE + ENCRYPTION + 0);<br />

writeReg(0xe0370734, AESBASE + DATABASE + ENCRYPTION + 0);<br />

//Wait 77 Clock cycles or for interrupt<br />

//READ_OUT<br />

Listing 2.1: Beispielcode zum Ansprechen des AES am Memory-Controller<br />

2.13 AES<br />

In symmetrischen Verschlüsselungsverfahren wird sowohl zur Verschlüsselung als auch<br />

zur Entschlüsselung der gleiche geheime Schlüssel benutzt. Ist einem Dritten dieser Schlüssel<br />

bekannt, so kann dieser den Kommunikationsprozess abhören und selbst verschlüsselte<br />

Datenpakete in Umlauf bringen. Ein bekanntes Beispiel für symmetrische Verschlüsselungsverfahren<br />

ist der DES-Algorithmus. Dieser wurde 2001 durch den AES abgelöst.<br />

Am häufigsten wird derzeit die 128-Bit-Version im Electronic Code Book (ECB)-Modus genutzt.<br />

Der ECB-Modus ist nicht rückgekoppelt, d.h. es wird jeder Datenblock unabhängig<br />

von anderen verarbeitet. So ist ein wahlfreier Zugriff auf verschlüsselte Blöcke möglich.<br />

Nachteilig ist, dass so gleiche Eingangsdaten zu gleichen Ausgangsdaten führen. Es gibt<br />

Anwendungsfälle, in denen der ECB-Modus nicht vermieden werden kann. Gehen z.B. in<br />

einem rückgekoppelten Modus wie Cipher Block Chaining (CBC) Datenpakete verloren, so<br />

22

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

ist das nachfolgende Datenpaket nicht mehr zu entschlüsseln. Insbesondere bei unzuverlässigen<br />

Verbindungen (wie Funk) ist daher der CBC-Modus nicht geeignet. In Systemen,<br />

die neben dem AES über eine CPU verfügen, können rückgekoppelte Modi so nachgebildet<br />

werden, dass zunächst die Verschlüsselung im AES-Coprozessor durchgeführt wird<br />

und anschließend die Operationen zur Rückkopplung in Software ausgeführt werden.<br />

2.13.1 Arithmetische Grundlagen<br />

Der Advanced Encryption Standard (AES) ist ein symmetrisches Verschlüsselungsverfahren.<br />

Im Gegensatz zu Stromchiffren, welche bit- oder byteorientiert arbeiten, werden beim<br />

AES jeweils Blöcke von 128 Bit (16 Byte) der Ver- oder Entschlüsselung unterzogen. Daher<br />

ist der AES eine Blockchiffre. Ein Datenblock wird in einer Matrix mit 4x4 Byte angeordnet<br />

(siehe Formel 2.1).<br />

⎡<br />

⎤<br />

32 88 31 e0<br />

3243f68a885a308d313198a2e0370734 ⇒ ⎢43 5a 31 37<br />

⎥<br />

⎣f6 30 98 07⎦ (2.1)<br />

8a 8d a2 34<br />

Nicht in jedem Fall wird die Länge eines zu verschlüsselnden Datenblocks (in Bit) einem<br />

ganzzahligen Vielfachen von 128 entsprechen. Hier müssen höhere Schichten durch die<br />

Auswahl geeigneter Padding-Algorithmen die tatsächliche Datenlänge an die geforderte<br />

Datenlänge anpassen.<br />

Durch das National Institute of Standards and Technology (NIST) [37] ist die Datenblocklänge<br />

von 128 Bit bei Schlüssellängen von 128, 192 sowie 256 Bit standardisiert. Dazu<br />

kommen Modi, die eine Kopplung zwischen verschiedenen Datenblöcken ermöglichen.<br />

Diese verhindern Attacken, bei denen einzelne Datenblöcke durch den Angreifer ausgetauscht<br />

werden. Ein grundlegender Unterschied zwischen den Versionen mit unterschiedlichen<br />

Schlüssellängen besteht in der Anwendung des Rundenschlüssels auf die Daten.<br />

Unabhängig von der Länge des Eingangsschlüssels werden in jeder AddKey-Operation<br />

der 128 Bit lange Datenblock mit einem 128 Bit langen Schlüsselteil verknüpft (siehe Abbildung<br />

2.5).<br />

Während für einen 128-Bit-Schlüssel jeweils der komplette Rundenschlüssel auf die 128<br />

Bit Daten angewendet wird, wird die Anwendung des 256-Bit-Schlüssels auf zwei Verarbeitungsrunden<br />

aufgeteilt. Bei jeder dieser Runden werden 128 Bit als Teilschlüssel verwendet.<br />

Ähnlich verhält es sich mit dem 192-Bit-Schlüssel. Die ersten 128 Bit des Rundenschlüssels<br />

werden auf die 128 Bit Daten angewandt. In der folgenden Runde wird<br />

zunächst aus dem Schlüssel der nächste Rundenschlüssel erzeugt. Anschließend werden<br />

die verbleibenden 64 Bit aus dem Initialschlüssel und die 64 Bit aus dem erzeugten<br />

Rundenschlüssel zusammen auf den 128-Bit-Datenblock angewendet. Aufgrund der Überlappungen<br />

eines Schlüssels auf mehrere Runden wird bei der Schlüssellänge von 192 Bit<br />

die Rundenzahl auf 12 und bei einem 256-Bit-Schlüssel auf 14 erhöht.<br />

23

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

128 Bit Datenpfad<br />

Runde n<br />

128 Bit<br />

128 Bit<br />

XOR<br />

Abbildung 2.5: Schlüsseladdition für 128 Bit<br />

Input key<br />

Calc<br />

key<br />

10 Rounds<br />

xor<br />

S-Box<br />

Shift<br />

row<br />

Mix<br />

Column<br />

Input data<br />

Output data<br />

Abbildung 2.6: Schematischer Aufbau der AES-Implementierung<br />

2.13.2 Algorithmusbeschreibung des AES<br />

Die Abbildung 2.6 zeigt schematisch den Ablauf der Verschlüsselung. Der Algorithmus wird<br />

für einen 128-Bit-Schlüssel in elf Runden auf die Daten angewendet. Jede dieser Runden<br />

besteht aus mehreren Teilschritten, wobei jeweils in der ersten und in der letzten Runde<br />

nicht alle Teilschritte ausgeführt werden. In den Beschreibungen der Teilschritte werden<br />

die Zeilen mit i (0 bis 3) sowie die Spalten mit j (0 bis 3) gekennzeichnet.<br />

• 1. Runde<br />

data=AddKey(data, key)<br />

• 2. Runde bis 10. Runde<br />

data=S-Box(data)<br />

data=ShiftRow(data)<br />

data=MixColumn(data)<br />

data=AddKey(data, key)<br />

• 11. Runde<br />

data=S-Box(data)<br />

data=ShiftRow(data)<br />

data=AddKey(data, key)<br />

24

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

AddKey<br />

Die Schlüsseladdition wird durch eine binäre XOR-Operation ausgeführt.<br />

S-Box Die Substitutions-Box (S-Box) ist eine nichtlineare Abbildung eines Bytes auf ein<br />

anderes. Dazu wird vom Eingangswert x in GF(2 8 ) das multiplikative Inverse x −1 (in Formel<br />

2.2 gilt: x −1 entspricht z0 bis z7) gebildet. Anschließend wird eine Matrixmultiplikation<br />

mit der vorgegebenen Matrix c ausgeführt und der Vektor (11000110) addiert (siehe Formel<br />

2.2). Die Ausführung der S-Box ist so gewählt, dass kein Bytewert auf sich selbst<br />

abgebildet wird, da dies ein potentieller Ansatzpunkt für Kryptoanalysen wäre. Da die S-<br />

Box-Transformation jeweils auf ein Byte angewendet wird, sind 16 dieser Transformationen<br />

pro Runde notwendig.<br />

⎡ ⎤ ⎡<br />

⎤ ⎡ ⎤ ⎡ ⎤<br />

y0 1 0 0 0 1 1 1 1 z0 1<br />

y1<br />

1 1 0 0 0 1 1 1<br />

z1<br />

1<br />

y2<br />

1 1 1 0 0 0 1 1<br />

z2<br />

0<br />

y3<br />

y4<br />

=<br />

1 1 1 1 0 0 0 1<br />

z3<br />

1 1 1 1 1 0 0 0<br />

z4<br />

+<br />

0<br />

0<br />

⎢y5<br />

⎥ ⎢0 1 1 1 1 1 0 0<br />

⎥ ⎢z5<br />

⎥ ⎢1<br />

⎥<br />

⎣y6⎦<br />

⎣0 0 1 1 1 1 1 0⎦<br />

⎣z6⎦<br />

⎣1⎦<br />

y7 0 0 0 1 1 1 1 1 z7 0<br />

(2.2)<br />

ShiftRow Die Bytes der Matrix rotieren in Abhängigkeit von der Zeilennummer i (i = 0 bis<br />

3) um i Stellen nach links (zyklisches Shiften, siehe Formel 2.3).<br />

⎡<br />

⎤ ⎡<br />

⎤<br />

00 01 02 03 00 01 02 03<br />

⎢10 11 12 13<br />

⎥<br />

⎣20 21 22 23⎦ ⇒ ⎢11 12 13 10<br />

⎥<br />

⎣22 23 20 21⎦ (2.3)<br />

30 31 32 33 33 30 31 32<br />

MixColumn Während die S-Box-Operation sich byteweise auswirkt, ist die MixColumn-<br />

Transformation eine Interaktion zwischen den 4 Bytes einer Spalte y0, j bis y3, j für j = 0<br />

bis 3 in GF(2 8 ). Dazu wird eine Matrixmultiplikation der Spalte j (j = 0 bis 3) mit der Matrix<br />

c ausgeführt (siehe Formel 2.4).<br />

⎡ ⎤ ⎡<br />

⎤ ⎡ ⎤<br />

y0, j 02 03 01 01 z0, j<br />

⎢y1, j<br />

⎥<br />

⎣y2, j⎦ ⇐ ⎢01 02 03 01<br />

⎥ ⎢z1, j<br />

⎥<br />

⎣01 01 02 03⎦<br />

⎣z2, j⎦ ∀j ∈ [0, 1, 2, 3] (2.4)<br />

y3, j 03 01 01 02 z3, j<br />

Schlüsselexpansion In jeder der elf Runden wird ein neuer Rundenschlüssel mit der<br />

Länge von 128 Bit benötigt. Der Schlüssel wird analog zu den Eingangsdaten auf eine<br />

4x4-Byte-Matrix abgebildet. Die Generierung eines neuen Rundenschlüssels besteht aus<br />

25

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

4 Teilschritten, in denen jeweils eine Spalte mit 4 Byte erzeugt wird. Gemäß Abbildung<br />

2.7 wird die erste Spalte des Folgeschlüssels durch die Ausführung einer Funktion F, die<br />

auf der S-Box basiert, auf die Spalte 3 sowie der XOR-Verknüpfung von F mit der Spalte<br />

0 gebildet. Die drei folgenden Spalten werden durch eine Addition der vorhergehenden<br />

Spalte mit der gleiche Spalte des vorhergehenden Schlüssels berechnet.<br />

Abbildung 2.7: Spaltenweise Generierung des nächsten Rundenschlüssels<br />

2.13.3 Implementierung<br />

Die im TSN genutzte Implementierung ver- und entschlüsselt Datenblöcke mit einer Länge<br />

von 128 Bit mit einem 128 Bit langen Schlüssel im ECB-Modus und ist auf niedrige bis<br />

mittlere Datenraten optimiert. Durch das 32-Bit-Dateninterface ist es notwendig, jeweils<br />

4 Datenblöcke á 32 Bit in das AES-Modul zu schreiben, um einen vollständigen 128-Bit-<br />

Datenblock zu erhalten. Vier weitere Schreiboperationen sind erforderlich, um den Schlüssel<br />

im AES-Modul abzulegen. Insgesamt werden so theoretisch nur 8 Adressen benötigt.<br />

Der zu Verfügung stehende Adressraum ist jedoch um einiges größer und wird auch ausgenutzt,<br />

um den notwendigen Kommandoblock und die dazugehörige Schreiboperation<br />

einzusparen. Dem AES-Modul muss mitgeteilt werden, ob die Daten zur Entschlüsselung<br />

oder zur Verschlüsselung abgeliefert wurden. Die Auswahl wird mit Hilfe eines Adressbits<br />

codiert. Die Daten zur Verschlüsselung werden beginnend mit der Adresse 0x90 und die<br />

Daten zur Entschlüsselung beginnend mit Adresse 0xA0 geschrieben. Für einen Datenblock<br />

werden insgesamt 78 Clocktakte benötigt, um die Daten zu ver- oder entschlüsseln.<br />

2.14 ECC<br />

Bei asymmetrischen Verschlüsselungsverfahren wird ein Schlüsselpaar, bestehend aus einem<br />

öffentlichen und einem privaten Schlüssel, eingesetzt. Der öffentliche Schlüssel des<br />

26

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

Empfängers ist frei zugänglich (z.B. über dessen Homepage) und die Daten können hiermit<br />

verschlüsselt werden. Der private Schlüssel ist geheim zu halten. Mit diesem kann<br />

die Nachricht wieder entschlüsselt werden. Aus dem öffentlichen Schlüssel kann der private<br />

Schlüssel nicht mit vernünftigem Aufwand errechnet werden, so dass verschlüsselte<br />

Nachrichten ausschließlich mit dem privaten Schlüssel zugänglich sind. Eine alternative<br />

Anwendung von asymmetrischen Verschlüsselungsverfahren ist das Unterschreiben einer<br />

Nachricht mit dem privaten Schlüssel. Mit dem entsprechenden öffentlichen Schlüssel<br />

kann dann die Echtheit dieser Signatur überprüft werden, da davon ausgegangen werden<br />

kann, dass einzig der Besitzer des privaten Schlüssels diese Nachricht so verschlüsseln<br />

beziehungsweise digital unterschreiben konnte. Ein asymmetrisches Verschlüsselungsverfahren<br />

eignet sich nicht für größere Datenmengen. Der Berechnungsaufwand für die Verschlüsselung<br />

der gleichen Datenmenge liegt mehrere Größenordnungen über dem für ein<br />

symmetrisches Verschlüsselungsverfahren.<br />

Das derzeit populärste Verfahren ist die RSA-Verschlüsselung, benannt nach den drei Erfindern<br />

Rivest, Shamir und Adleman [44]. Die Elliptic Curve Cryptography (ECC) auf Basis<br />

elliptischer Kurven ist ein modernerer alternativer Verschlüsselungsansatz. Im Vergleich<br />

zum RSA bietet der ECC-Ansatz einen gleichwertigen Sicherheitsgrad bei wesentlich kürzeren<br />

Schlüssellängen. Soll zum Beispiel die Sicherheit von verschlüsselten Daten für<br />

die nächsten 20 Jahre gewahrt sein, ist empfohlen, für RSA 2048 Bit lange Schlüssel zu<br />

nutzen. Das ECC-Verfahren erreicht den gleichen Grad an Sicherheit schon mit 233 Bit<br />

langen Schlüsseln [29]. Kürzere Schlüssel sind besonders wichtig, wenn Kryptographie<br />

auf mobilen Geräten mit wenig Speicher und begrenzter Rechenstärke eingesetzt wird.<br />

2.14.1 Arithmetische Grundlagen<br />

ECC ist ein kryptographisches Verfahren, das mit 2-dimensionalen Punkten (x, y) auf einer<br />

elliptischen Kurve arbeitet. Die x- und y-Koordinaten sind Elemente eines finiten Feldes,<br />

des so genannten Basisfeldes. Auf den Punkten dieser Kurve sind algebraische Operationen,<br />

wie die Addition zweier Punkte definiert. Die wichtigste, kryptographisch eingesetzte<br />

Operation ist die k*P-Multiplikation, bei der ein Punkt mit einer ganzen Zahl multipliziert<br />

wird. Diese Operation ist recht einfach zu berechnen. Die Umkehroperation ist allerdings<br />

nicht in polynomineller Zeit zu lösen.<br />

Für das ECC-Verfahren eignen sich zwei Arten von generellen Basisfeldern: Restklassenfelder<br />

basierend auf einer großen Primzahl (GF(p)) und Restklassenfelder basierend auf<br />

erweiterten Binärfeldern (GF(2 m )). Beide Arten gelten als sicher. Geeignete Parameter<br />

wurden bereits von Standardisierungsgremien empfohlen. Für energie- und flächeneffiziente<br />

Implementierungen in Hardware eigenen sich insbesondere die binären Kurven, da<br />

deren Arithmetik eine vereinfachte Darstellung in Hardware (GF(2 m )) erlaubt. Desweiteren<br />

sind additive Operationen einfache XOR-Operationen und benötigen daher keine Überträge.<br />

Diese Eigenschaften begründen die Entscheidung, bei dem Design binäre Felder als<br />

Basisfeld zu nutzen.<br />

ECC-Operationen nutzen intensiv Operationen des Basisfelds. Zum Beispiel benötigt eine<br />

k*P-Multiplikation in (GF(2 233 )) etwa 1500 Feldmultiplikationen. Deshalb sind genaue<br />

27

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

Untersuchungen der Operationen im Basisfeld für eine effiziente ECC-Implementierung<br />

unumgänglich. Bei den Betrachtungen der mathematischen Grundlagen im Basisfeld der<br />

elliptischen Kurve stellen sich insbesondere folgende Operationen als kritisch heraus:<br />

• Feldmultiplikation<br />

• modulare Reduktion.<br />

2.14.2 Multiplizierer<br />

Die Feldmultiplikation ist die mit Abstand aufwändigste Operation im Basisfeld. Eine 256-<br />

Bit-Multiplikation benötigt zum Beispiel je über 65000 XOR- und AND-Operationen, wenn<br />

sie nach der Methode der klassischen Schulmultiplikation ausgeführt würde. In der Literatur<br />

werden verbesserte Verfahren wie die klassische Karatsuba-Multiplikation und die iterative<br />

Karatsuba-Multiplikation vorgestellt [14]. Letztere verringert vor allem die Anzahl der<br />

notwendigen AND-Operationen (auf 6561) aber kaum die Anzahl der XOR-Operationen<br />

(62000). In dem Design wird eine rekursive Anwendung der iterativen Karatsuba-Methode<br />

(RAIK) [39], die auch die Anzahl der XOR-Operationen (auf unter 43000) reduzieren<br />

kann, genutzt. Bei den rekursiven Karatsuba-Methoden wird eine Multiplikation durch kleinere<br />

Multiplikationen mit kürzerer Bitlänge ersetzt, die dann wiederum mit der Karatsuba-<br />

Methode gelöst wird. Da festgestellt wurde, dass sich für kürzere Multiplikationen mit Bitlängen<br />

von unter 8 Bit eine weitere rekursive Zerlegung nach der Karatsuba-Methode nicht<br />

positiv auf den Gesamtaufwand auswirkt, werden für diese kurzen Multiplikationen andere<br />

Verfahren angewandt. Als Beispiel sei hier die klassische Schulmultiplikation genannt,<br />

wodurch der Gesamtaufwand für rekursive Multiplikation signifikant reduziert wird. Diese<br />

theoretischen Betrachtungen der polynominellen Multiplikation sind die Basis für eine effiziente<br />

Implementierung dieser Operation in Hardware, wie sie in dem Design realisiert<br />

wurden. Der Ansatz ist detaillierter in [45] diskutiert.<br />

2.14.3 Reduktion<br />

Die zweite kritische Operation ist die Reduktion. Diese Operation muss nach jeder Feldmultiplikation<br />

ausgeführt werden. Das ist begründet durch den finiten Charakter des Basisfeldes.<br />

Die Multiplikation zweier m Bit langen Faktoren ergibt ein 2m-1 Bit langes Produkt<br />

(siehe Abbildung 2.8). Da die Elemente des Feldes genau m Bit lang sind, muss zu dem<br />

2m-1 Bit langen Element ein in dem Feld äquivalentes Element mit der Länge m berechnet<br />

werden. Ein klassisches Verfahren für diese Operation ist die Division mit Rest durch das<br />

Generatorpolynom, wobei der Rest der Division das äquivalente Element darstellt.<br />

Ähnlich wie eine Division in „normalen“ Zahlensystemen ist auch die Division in GF(2 m )<br />

sehr komplex und deshalb nach jeder Feldmultiplikation nicht sinnvoll. In der Literatur werden<br />

Verfahren beschrieben, welche die Reduktion als eine einfache Abbildung mit konstantem<br />

Aufwand herausstellen. Diese Verfahren können sowohl in Software- als auch<br />

in Hardwareimplementierungen angewendet werden. Das Problem bei dieser Vorgehens-<br />

28

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

weise ist, dass für jedes Feld und damit für jede Schlüssellänge eine spezielle Abbildung<br />

generiert werden muss. Hier ergibt sich das Problem der Reduktion: Entweder man hat<br />

eine schnelle, effiziente Implementierung, die aber nur eine bestimmte Kurve unterstützt<br />

oder einen komplexen Algorithmus, der dann aber nicht an bestimmte Kurven gebunden<br />

ist.<br />

In dem Design wurde sich auf die Beschleunigung einer einzigen Kurve konzentriert. Ziel<br />

war es, eine möglichst schnelle und kleine Hardwarelösung für die ECC-Operation mit<br />

einer Bitbreite von 233 Bit zu realisieren. Hierfür kann das Reduktionspolynom direkt in<br />

dem Design verdrahtet werden. Die Reduktionsoperation benötigt somit 0,034 mm 2 Siliziumfläche,<br />

während eine flexible Lösung die Fläche und auch die letztendliche Laufzeit<br />

signifikant erhöht hätten.<br />

Die Kurve mit Operanden von 233 Bit ist seitens der NIST unter der Bezeichnung „B 233“<br />

standardisiert [13]. Diese Kurve wurde ausgewählt, da die Sicherheit in etwa der Sicherheit<br />

des eingesetzten, symmetrischen Verschlüsselungsverfahren AES entspricht [6a].<br />

Abbildung 2.8: Da das Ergebnis einer Multiplikation länger als die maximale<br />

Feldlänge ist, benötigt man einen Reduktionsschritt, der das<br />

Ergebnis innerhalb des Feldes reduziert.<br />

2.14.4 System-Design<br />

Im ECC-Design wurde eine Prozessorarchitektur gewählt, die der Transport-getriggerten<br />

Architektur (TTA) entspricht. Alle Funktionseinheiten (siehe Abbildung 2.9), also Multiplizierer<br />

(MUL), Addierer, Quadrierer (beides als Teil der Arithmetisch-Logischen-Unit (ALU))<br />

sowie Register (Register File) sind mit einem 233 Bit breiten Bus verbunden. Der Zugriff<br />

auf den Bus wird von einer zentralen Kontrollsteuerung (Controller) geregelt. In dieser Einheit<br />

befindet sich das fest verdrahtete Ausführungsprogramm der ECC-Einheit. Die Testbit-<br />

Einheit verbindet die ansonsten komplett getrennten Datenfluss- und Kontrollflussteile der<br />

Schaltung. Diese Testbit-Einheit überprüft, ob ein bestimmtes Bit auf dem Datenbus gesetzt<br />

wurde. Bei der TTA sind die Operationen der Funktionsblöcke durch den Bustransfer<br />

getriggert. Der Start einer Multiplikation wird beispielsweise aktiviert, wenn zwei Datenworte<br />

(die Faktoren) zum Multiplizierer transportiert wurden. Späteres Lesen vom Multiplizierer<br />

liefert dann automatisch das Produkt. Diese Art der Architektur ist sehr einfach, da<br />

Komponenten hinzugefügt oder entfernt werden können ohne andere Komponenten oder<br />

Kontrollstrukturen ändern zu müssen. Neben dieser Flexibilität erlaubt diese Architektur eine<br />

explizite Parallelität. In der Zeit, in der beispielsweise eine Multiplikation berechnet wird,<br />

können weitere Operationen, wie Additionen oder Registertransfer, ausgeführt werden.<br />

29

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

Das Programm in der Kontrolleinheit führt die Punktmultiplikation entsprechend dem Lopez-Dahab-Algorithmus<br />

[32] aus. Dieser Algorithmus erlaubt die Ausführung einer EC<br />

Punktmultiplikation (ECPM) mit lediglich einer Division im Basisfeld. Diese eine Division<br />

wird mittels des Itoh-Tsujii-Ansatzes [22] berechnet. Durch den im Design vorhandenen<br />

schnellen Quadrierer und Multiplizierer ist dieser Algorithmus schneller und ressourcensparender<br />

als zum Beispiel der alternative erweiterte Euklidische Algorithmus. Die Algorithmen<br />

sind Teil des fest verdrahteten Programms in der Kontrolleinheit, die den Fluss der<br />

Daten zwischen den Rechen- und Registereinheiten steuert.<br />

Die Flexibilität des Designs bezüglich der Funktionseinheiten erlaubt es, eine praxisnahe<br />

„Design-Space-Exploration“ durchzuführen. Mittels dieser Exploration wird der Einfluss<br />

der Anzahl und der Geschwindigkeit der einzelnen Funktionseinheiten auf die Leistung<br />

des gesamten Systems ermittelt. Die Untersuchung ergab, dass die Geschwindigkeit der<br />

Feldmultiplikation die wichtigste Einflussgröße für die Leistung des Gesamtsystems darstellt.<br />

Mehrere Multipliziereinheiten können allerdings überraschenderweise die Leistung<br />

nicht entscheidend verbessern. Deshalb werden letztlich drei Designs für die 233-Bit-ECC-<br />

Beschleunigung näher untersucht. Deren wesentlicher Unterschied liegt in der Geschwindigkeit<br />

und damit der Größe des Feldmultiplizierers.<br />

Für eine Feldmultiplikation erfordert das schnellste und damit auch das größte Design drei<br />

Taktzyklen. Das mittelgroße Design benötigt neun und das kleinste 27 Taktzyklen. Die Gesamtzeit<br />

für eine ECPM beträgt 60 µs für das schnellste, 80 µs für das mittlere und 230<br />

µs für das kleinste Design. Die schnelleren beiden Designs gehören zu den schnellsten<br />

bisher veröffentlichten Implementierungen. Dabei ist die erforderliche Siliziumfläche von<br />

2,1 mm 2 für das größte bis zu 1,3 mm 2 für das kleinste Design im Vergleich zu anderen<br />

Implementierungen mit vergleichbarer Geschwindigkeit sehr gering. Die benötigte Energie<br />

der vorgestellten Designs für eine ECPM ist geringer als bei allen anderen bisher veröffentlichten<br />

Implementierungen. Entsprechend dem 233-Bit-Design wurden auch Designs<br />

für andere elliptische Kurven bis zu 571 Bit implementiert, vermessen und verglichen. Abbildung<br />

2.10 zeigt die verschiedene Flächen und Energieverbräuche für eine ECPM der<br />

untersuchten Designs von 163 bis 571 Bit.<br />

Für den TSN wurde die 233-Bit-Implementierung mit der mittleren Geschwindigkeit, d.h. 9<br />

Clockzyklen pro Feldmultiplikation, gewählt.<br />

Dies wird dadurch begründet, dass die 233-Bit-Implementierung das beste Verhältnis zwischen<br />

Fläche und Energie und Leistung (Geschwindigkeit) verspricht und dabei eine hohe<br />

Sicherheit bietet. Für eine noch höhere Sicherheit besteht die Möglichkeit der Nutzung<br />

größerer Schlüssellängen, wobei das entsprechend mehr Fläche in der Schaltung, mehr<br />

Berechnungszeit und auch mehr Stromverbrauch implizieren würde.<br />

Die 233-Bit-Implementierung wurde bereits in einem System-on-Chip (SoC) integriert, das<br />

neben einem eingebetteten 32-Bit-Prozessor Hardwareblöcke für die Verarbeitung von<br />

Netzwerkprotokollen und symmetrischer Verschlüsselung umfasst. Auf diesem Chip, der<br />

bereits im IHP in 0,25-µm-CMOS-Technologie gefertigt wurde, kann die Leistung des Hardwaredesigns<br />

gut mit einer alternativen Softwareimplementierung (MIRACL [47]), die auf<br />

dem eingebettetem Prozessor läuft, verglichen werden. Im Vergleich mit der Softwareim-<br />

30

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

plementierung ist die dedizierte Hardware hierbei 1000-mal schneller und benötigt insgesamt<br />

ein 500stel der Energie für eine 233-Bit-ECPM.<br />

Abbildung 2.9: Blockschaltbild des 233-Bit-ECC-Beschleunigers. Ein 233 Bit<br />

breiter, von einer Controller-Einheit kontrollierter Bus verbindet die<br />

Rechen- und Registereinheiten.<br />

Abbildung 2.10: Resultate der verschiedenen ECC-Beschleuniger-Schaltungen. Die<br />

Balken zeigen die benutzte Siliziumfläche. Die Linien entsprechen<br />

dem Energieverbrauch.<br />

2.14.5 Parameter im TSN<br />

Im TSN befindet sich eine Recheneinheit für die 233-Bit-Elliptische-Kurven-Punkt-Multiplikation<br />

im Feld (GF(2 233 )). Das Design der ECC-Recheneinheit entspricht derjenigen, die<br />

in Abbildung 2.9 dargestellt ist. Es beinhaltet:<br />

31

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

• Acht 233-Bit-Register, von denen vier von außen zugreifbar sind, die anderen vier<br />

sind für die interne Berechnung.<br />

• Eine Arithmetisch-Logische-Einheit (ALU), die die Addition und die Quadrierungsoperation<br />

ausführt. Beide Operationen können innerhalb eines Taktzyklus berechnet<br />

werden.<br />

• Einen Multiplizierer, der die Multiplikation im Basisfeld (GF(2 233 )) inklusive der Reduktion<br />

ausführt. Basierend auf den Ergebnissen der Design-Space-Exploration haben<br />

wir uns für das Design, welches neun Taktzyklen pro Multiplikation benötigt (also das<br />

4-Segment-Design), entschieden. Eine detaillierte Untersuchung des Multiplizierers<br />

kann in [14] gefunden werden.<br />

• Einen Controller und Testbit-Einheit, die den Datenfluss steuern. Das Programm<br />

selbst ist Teil des VHDL-Codes und ist optimiert auf die Busstruktur und den gewählten<br />

Multiplizierer.<br />

Sowohl die Quadrierungseinheit als auch der Multiplizierer führen automatisch und innerhalb<br />

eines Taktzyklus die fest verdrahtete Reduktionsoperation mit dem für das Feld standardisierten<br />

Reduktionspolynom (r(x) = x 233 + x 74 + 1) aus. Die Ausführung des Lopez-<br />

Dahab-Algorithmus benötigt<br />

• 232 mal 55 (12760) Taktzyklen für die Punktmultiplikation<br />

• 314 Taktzyklen für die Inversion im Basisfeld<br />

• 119 Taktzyklen für die Koordination und Bereitstellung des Ergebnisses,<br />

also insgesamt 13193 Taktzyklen. Die ECC-Punktmultiplikation wird gestartet, indem der<br />

Faktor k, die Koordinaten des Basispunktes x und y und der Parameter der Kurve b in<br />

die entsprechenden Register (siehe Anhang) geschrieben werden. Anschließend wird das<br />

32-Bit-Kommandowort, welches die Gesamtoperation startet an die Kontrolleinheit übergeben.<br />

2.15 SHA-1 / PRNG<br />

Das SHA-1-Modul ist nach den NIST-Standards FIPS 180-1 [34], FIPS 186-1 [35] und FIPS<br />

186-2 [36] aufgebaut. Der SHA-1 ist ein Teil des Digital Signature Standard (DSS), der eindeutige<br />

Hashwerte für einen Datenblock erzeugt. Anhand dieser kann man feststellen, ob<br />

ein Datenblock nachträglich verändert wurde oder nicht. Weiterhin kann die Komponente<br />

als Pseudozufallszahlengenerator (engl. Pseudo Random Number Generator (PRNG))<br />

verwendet werden. Derartige Zufallszahlen werden für viele kryptographische Algorithmen,<br />

wie zum Beispiel ElGamal, benötigt. In Abbildung 2.11 ist das Blockdiagramm des SHA-1-<br />

Moduls dargestellt. Der zugrunde liegende Algorithmus und die Funktionalität der Komponente<br />

werden in den folgenden Abschnitten genauer beschrieben. Die Implementierung<br />

des SHA-1 ist auf 32-Bit-Lese- und Schreibzugriffe ausgelegt. Für einen einfachen Zugriff<br />

32

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

wurde das Modul mit einer Schnittstelle mit einem memory-like Interface ausgestattet. Die<br />

Implementierung setzt nicht den kompletten SHA-1 um. Sie enthält nur die Funktion G,<br />

die den Hauptteil des Algorithmus darstellt. Die restlichen Funktionen, wie zum Beispiel<br />

Bitstuffing, werden sinnvollerweise in höheren Schichten umgesetzt.<br />

Software<br />

Split data into 512-Bit blocks;<br />

Bitstuffing for the last data block;<br />

Write and read controlregister;<br />

Write data to registers H0 to H4(160-bit KEY);<br />

Write data and W0 to W15 (512-bit data block);<br />

Function G<br />

Function K<br />

Function f<br />

Hardware<br />

Algorithm of G<br />

Software<br />

Read registers H0 to H4 (160-bit Signature of the data);<br />

Abbildung 2.11: Ablauf der Signatur mit Hilfe von Soft- und Hardware<br />

2.15.1 Secure Hash Algorithmus<br />

Für den SHA-1 werden die Daten, über die der Hashwert gebildet werden soll, in 512 Bit<br />

lange Blöcke zerlegt. Lässt sich das Datum nicht in ein Vielfaches von 512 zerlegen, muss<br />

der letzte Block aufgefüllt werden. Dies wird als „Bitstuffing“ bezeichnet. Zur Realisierung<br />

sind die letzten 64 Bit des letzten Datenblocks reserviert. Sie enthalten die Länge der zu<br />

signierenden Nachricht. Mit Hilfe dieses Wertes kann festgestellt werden, wie viele Bits des<br />

letzten Blocks nicht mehr für die Nachricht benötigt werden und aufgefüllt werden müssen.<br />

Das Auffüllen wird umgesetzt, indem nach dem letzten für die Nachricht relevanten Bit eine<br />

binäre „1“ eingeführt wird. Die restlichen Bitstellen werden mit „0“ belegt.<br />

Für die Integritätsprüfung mit Hilfe des SHA-1 gibt es zwei unterschiedliche Verfahren.<br />

Das erste Verfahren basiert darauf, dass beide Kommunikationspartner einen geheimen,<br />

frei gewählten Schlüssel kennen. Die zu signierende Nachricht wird dabei zunächst auf ein<br />

Vielfaches von 512 Bit vervollständigt und anschließend in 512 Bit lange Blöcke zerlegt.<br />

Diese werden dann blockweise an den SHA-1 übergeben. Neben den Datenblöcken benötigt<br />

der Algorithmus einen definierten Startwert. Dieser ist 160 Bit lang und wird als der<br />

geheime „Schlüssel“(KEY) bezeichnet. Er sollte nur den Kommunikationspartnern bekannt<br />

sein, da mit diesem eine eindeutige Signatur für die Daten erzeugt wird und diese auch<br />

verifiziert werden kann. Die erstellte Signatur wird mit den Daten übertragen. Der Empfänger<br />

führt ebenfalls den SHA-1 mit dem gleichen Schlüssel auf die empfangenen Daten<br />

aus. Wurden die Daten bei der Übertragung durch Dritte verändert, führt dies zu einer anderen<br />

Signatur. Derartige Veränderungen werden dann beim Vergleich beider Signaturen<br />

entdeckt. Um eine sichere Signierung der Daten zu gewährleisten, muss der Schlüssel<br />

für den SHA-1 zwischen den Kommunikationspartnern geheim übertragen werden. Dafür<br />

33

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

werden Schlüsselaustauschverfahren, wie zum Beispiel das Verfahren von ElGamal, benötigt.<br />

Mit deren Hilfe wird verhindert, dass Dritte unerlaubt in den Besitz des geheimen<br />

Schlüssels kommen.<br />

Die zweite Möglichkeit zur Signierung von Daten mittels SHA-1 besteht in der Nutzung des<br />

ECC als asymmetrisches Verfahren, so dass der Sender der Nachricht einen privaten und<br />

einen öffentlichen Schlüssel besitzt. Der private Schlüssel dient der Signierung durch den<br />

Absender und der öffentliche Schlüssel der Prüfung der Signatur durch den Empfänger.<br />

Dieses Verfahren wird als „ECDSA“ bezeichnet und ist unter ANSI X9.62 standardisiert.<br />

Hierbei fungiert der sogenannte „Key“ als standardisierter Initialisierungswert (h0 bis h4).<br />

Im Folgenden wird der Ablauf und der Aufbau des Secure-Hash-Algorithmus vorgestellt.<br />

Wie bereits erläutert, erhält der Algorithmus als Eingabe die zu signierenden Daten und<br />

den geheimen Schlüssel. Zu Beginn wird das „Bitstuffing“ für die zu signierenden Daten<br />

ausgeführt. Der letzte Block wird der oben beschriebenen Vorgehensweise nach mit einer<br />

„1“ und „0“ aufgefüllt. Diese Vorverarbeitung der Daten wird vorzugsweise in Software<br />

realisiert, da hier kaum eine Optimierung durch die Verwendung von Hardware erreicht<br />

werden kann. Im Anschluss wird der geheime 160-Bit-Schlüssel in die entsprechenden<br />

Register (H-Register) des SHA-1-Hardware-Moduls geschrieben. Dazu ist es notwendig,<br />

den Schlüssel in fünf 32-Bit-Blöcke zu unterteilen. Der Datenblock wird in sechzehn 32-Bit-<br />

Blöcke aufgeteilt und in die W-Register der Komponente geschrieben. Nachdem das letzte<br />

der W-Register geschrieben wurde, beginnt die SHA-1-Hardwarekomponente mit der Generierung<br />

der Signatur. Ist der Algorithmus nach 80 Taktzyklen abgeschlossen, kann der<br />

nächste Datenblock in die W-Register geschrieben werden. Dies wird für alle 512-Bit-Blöcke<br />

durchgeführt. Nachdem alle Daten die SHA-1-Komponente passiert haben, befindet<br />

sich in den H-Registern des Moduls die Signatur des Datenpakets. Diese kann nun ausgelesen<br />

werden, um zum Beispiel mit der Nachricht verschickt zu werden. Der innere Aufbau<br />

der Hardwarekomponenten umfasst drei Funktionen, die zur Generierung der Signatur benötigt<br />

werden. Bei diesen handelt es sich um die Funktionen f, K und G. In Abbildung 2.11<br />

ist der Aufbau des SHA-1 dargestellt mit der Unterteilung nach Soft- und Hardware.<br />

Die Arbeitsweise dieser drei Funktionen f, K und G steht in Abhängigkeit zur Anzahl der<br />

verstrichenen Taktzyklen. Die Funktion G stellt die Hauptfunktion des SHA-1 dar. Mit ihr<br />

wird aus dem eingegebenen 160-Bit-Schlüssel und dem 512 Bit langen Datenblock die<br />

Signatur erzeugt. Die Funktion K liefert in Abhängigkeit der aktuellen Laufzeit des Algorithmus<br />

eine Konstante, die in der Funktion G genutzt wird, um einen Teil der Zwischenergebnisse<br />

für die Signaturerzeugung zu generieren. Diese Zwischenergebnisse werden nach<br />

jedem Takt in den Registern A bis E abgelegt. Nach 80 Takten wird der Inhalt dieser Register<br />

in den H-Registern verrechnet. Diese enthalten dann die Signatur des Datenblocks.<br />

Die Funktion f erzeugt, ebenfalls in Abhängigkeit von der aktuellen Taktanzahl, einen Teil<br />

dieser Zwischenergebnisse und bezieht bei der Berechnung ihres neuen Wertes die Zwischenergebnisse<br />

in den Registern B, C und D des vorherigen Taktes ein. Listing 2.2 zeigt<br />

den Aufbau der Funktionen f und K.<br />

f(j) with 0

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

f(j,B,C,D)= (B and C) or (B and D) or (C and D) for 40

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

Zu Beginn jedes der 80 Takte der Funktion G ermitteln die Funktionen f und K ihre Zwischenergebnisse.<br />

Als Ergebnis von K wird eine 32 Bit lange Konstante ausgegeben, die in<br />

Abhängigkeit der aktuellen Anzahl von Takten bestimmt wird. Die Funktion F ermittelt ihr<br />

32-Bit-Ergebnis aus der Verknüpfung der Werte aus den Registern B, C und D. Zu Beginn<br />

des Algorithmus enthalten diese, wie die H-Register auch, den geheimen Schlüssel und<br />

im weiteren Verlauf die Zwischenergebnisse der Signatur. Der Aufbau der Verknüpfung ist<br />

ebenfalls von der aktuellen Taktanzahl abhängig. Nachdem diese beiden Funktionen ihre<br />

Ergebnisse generiert haben, startet die Funktion G. Als erstes wird ein weiteres Zwischenergebnis<br />

in Abhängigkeit von der aktuellen Taktzahl ermittelt. Dieses entspricht entweder<br />

dem Inhalt des Registers W0 oder der XOR-Verknüpfung der Register W13, W8, W2 und<br />

W0 mit einer zusätzlichen Bitschiebeoperation des Ergebnisses nach links (in Richtung der<br />

höherwertigen Bits). Im Anschluss werden alle W-Register um ein Register nach rechts,<br />

das heißt in Richtung der niederwertigen Register, geschoben. Der Wert des Registers W0<br />

wird in dem Register W15 abgelegt.<br />

Aus all den bis zu diesem Zeitpunkt ermittelten Werten wird durch Addition der Ergebnisse<br />

das Zwischenergebnis eines Teilblocks der Signatur ermittelt. Dessen Wert setzt sich aus<br />

einer fünfmaligen Bitschiebeoperation des Registerinhalts von A nach links zusammen.<br />

Auf diesen Wert werden anschließend der Registerinhalt von E sowie die Ergebnisse von<br />

f, K und der Verknüpfung der drei W-Register addiert. Dieses Ergebnis wird später in dem<br />

Register A abgelegt. Zuvor werden die Inhalte der Register B bis E um ein Register nach<br />

links verschoben. Der neue Wert des Registers C wird zudem noch um 30 Bit nach links<br />

verschoben. Nun enthält das Register A den zuvor berechneten Wert.<br />

Nach 80 Takten werden die Zwischenergebnisse aus den Registern A bis E mit den Inhalten<br />

der H-Register addiert. Der Wert in Register B wird zudem noch um 30 Bit nach<br />

links verschoben. In den H-Registern steht nun die Signatur der bis dahin behandelten<br />

Datenblöcke. Die Signatur kann über Software aus den H-Registern ausgelesen werden.<br />

2.15.2 Pseudo Random Number Generator (PRNG)<br />

Es besteht die Möglichkeit, das SHA-1-Modul als Generator für Pseudozufallszahlen zu<br />

verwenden. Dies wird in FIPS 186-2 [36] genauer erläutert. Für die Generierung derartiger<br />

Zahlen mit Hilfe des Secure Hash Algorithmus ist es zu Beginn notwendig einen Schlüssel<br />

und einen Datenblock in die entsprechenden H- und W-Register des Moduls zu schreiben.<br />

Die Kombination aus Schlüssel und Daten bilden den Ausgangswert (Seed) für die<br />

Generierung der Pseudozufallszahl. Verwendet man stets den gleichen Seed, wird immer<br />

eine identische Folge von Zufallszahlen erzeugt. Aufgrund der Wiederholbarkeit nennt<br />