Abschlussbericht

Abschlussbericht

Abschlussbericht

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

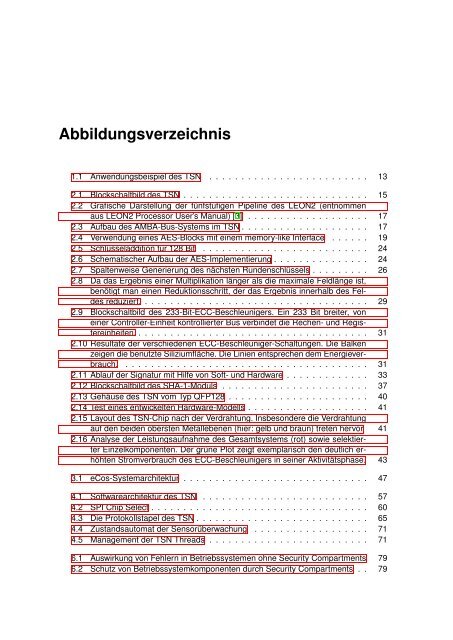

Abbildungsverzeichnis<br />

1.1 Anwendungsbeispiel des TSN . . . . . . . . . . . . . . . . . . . . . . . . . 13<br />

2.1 Blockschaltbild des TSN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15<br />

2.2 Grafische Darstellung der fünfstufigen Pipeline des LEON2 (entnommen<br />

aus LEON2 Processor User’s Manual) [3] . . . . . . . . . . . . . . . . . . . 17<br />

2.3 Aufbau des AMBA-Bus-Systems im TSN . . . . . . . . . . . . . . . . . . . . 17<br />

2.4 Verwendung eines AES-Blocks mit einem memory-like Interface . . . . . . 19<br />

2.5 Schlüsseladdition für 128 Bit . . . . . . . . . . . . . . . . . . . . . . . . . . 24<br />

2.6 Schematischer Aufbau der AES-Implementierung . . . . . . . . . . . . . . . 24<br />

2.7 Spaltenweise Generierung des nächsten Rundenschlüssels . . . . . . . . . 26<br />

2.8 Da das Ergebnis einer Multiplikation länger als die maximale Feldlänge ist,<br />

benötigt man einen Reduktionsschritt, der das Ergebnis innerhalb des Feldes<br />

reduziert. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29<br />

2.9 Blockschaltbild des 233-Bit-ECC-Beschleunigers. Ein 233 Bit breiter, von<br />

einer Controller-Einheit kontrollierter Bus verbindet die Rechen- und Registereinheiten.<br />

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31<br />

2.10 Resultate der verschiedenen ECC-Beschleuniger-Schaltungen. Die Balken<br />

zeigen die benutzte Siliziumfläche. Die Linien entsprechen dem Energieverbrauch.<br />

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31<br />

2.11 Ablauf der Signatur mit Hilfe von Soft- und Hardware . . . . . . . . . . . . . 33<br />

2.12 Blockschaltbild des SHA-1-Moduls . . . . . . . . . . . . . . . . . . . . . . . 37<br />

2.13 Gehäuse des TSN vom Typ QFP128 . . . . . . . . . . . . . . . . . . . . . . 40<br />

2.14 Test eines entwickelten Hardware-Modells . . . . . . . . . . . . . . . . . . . 41<br />

2.15 Layout des TSN-Chip nach der Verdrahtung. Insbesondere die Verdrahtung<br />

auf den beiden obersten Metallebenen (hier: gelb und braun) treten hervor 41<br />

2.16 Analyse der Leistungsaufnahme des Gesamtsystems (rot) sowie selektierter<br />

Einzelkomponenten. Der grüne Plot zeigt exemplarisch den deutlich erhöhten<br />

Stromverbrauch des ECC-Beschleunigers in seiner Aktivitätsphase. 43<br />

3.1 eCos-Systemarchitektur . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47<br />

4.1 Softwarearchitektur des TSN . . . . . . . . . . . . . . . . . . . . . . . . . . 57<br />

4.2 SPI Chip Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60<br />

4.3 Die Protokollstapel des TSN . . . . . . . . . . . . . . . . . . . . . . . . . . . 65<br />

4.4 Zustandsautomat der Sensorüberwachung . . . . . . . . . . . . . . . . . . 71<br />

4.5 Management der TSN Threads . . . . . . . . . . . . . . . . . . . . . . . . . 71<br />

6.1 Auswirkung von Fehlern in Betriebssystemen ohne Security Compartments 79<br />

6.2 Schutz von Betriebssystemkomponenten durch Security Compartments . . 79