Abschlussbericht

Abschlussbericht

Abschlussbericht

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

Position eine „0“, wird die entsprechende Komponente neu gestartet und im Anschluss das<br />

Bit im Reset-Controller wieder auf „1“ gesetzt.<br />

Der Controller sollte als Memory-Mapped-I/O Komponente, analog zu den kryptografischen<br />

Modulen, in das System integriert werden. Dadurch kann das Lesen und Schreiben<br />

des Controllers durch einfache Speicherzugriffe realisiert werden.<br />

Einführen von Clock-Gating<br />

Der TSN verwendet in der aktuellen Version kein Clock-Gating, so dass das Clock-Signal<br />

stets zu jeder Zeit zu jeder Komponente weitergeleitet wird. Das Clock-Gating wird dazu<br />

benutzt, den Systemtakt an den Registern der Schaltung zu unterbrechen, um somit das<br />

interne Schalten der Flipflops zu verhindern und Energie zu sparen. Dieses Unterbrechen<br />

wird immer dann eingesetzt, wenn der aktuelle Zustand des Systems den Zugriff auf die<br />

Register nicht zulässt.<br />

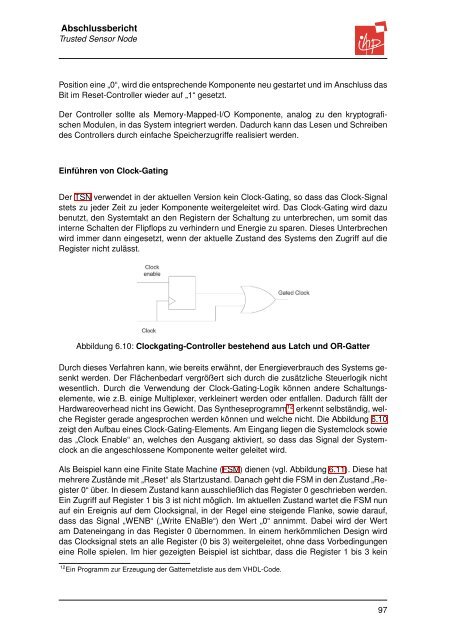

Abbildung 6.10: Clockgating-Controller bestehend aus Latch und OR-Gatter<br />

Durch dieses Verfahren kann, wie bereits erwähnt, der Energieverbrauch des Systems gesenkt<br />

werden. Der Flächenbedarf vergrößert sich durch die zusätzliche Steuerlogik nicht<br />

wesentlich. Durch die Verwendung der Clock-Gating-Logik können andere Schaltungselemente,<br />

wie z.B. einige Multiplexer, verkleinert werden oder entfallen. Dadurch fällt der<br />

Hardwareoverhead nicht ins Gewicht. Das Syntheseprogramm 12 erkennt selbständig, welche<br />

Register gerade angesprochen werden können und welche nicht. Die Abbildung 6.10<br />

zeigt den Aufbau eines Clock-Gating-Elements. Am Eingang liegen die Systemclock sowie<br />

das „Clock Enable“ an, welches den Ausgang aktiviert, so dass das Signal der Systemclock<br />

an die angeschlossene Komponente weiter geleitet wird.<br />

Als Beispiel kann eine Finite State Machine (FSM) dienen (vgl. Abbildung 6.11). Diese hat<br />

mehrere Zustände mit „Reset“ als Startzustand. Danach geht die FSM in den Zustand „Register<br />

0“ über. In diesem Zustand kann ausschließlich das Register 0 geschrieben werden.<br />

Ein Zugriff auf Register 1 bis 3 ist nicht möglich. Im aktuellen Zustand wartet die FSM nun<br />

auf ein Ereignis auf dem Clocksignal, in der Regel eine steigende Flanke, sowie darauf,<br />

dass das Signal „WENB“ („Write ENaBle“) den Wert „0“ annimmt. Dabei wird der Wert<br />

am Dateneingang in das Register 0 übernommen. In einem herkömmlichen Design wird<br />

das Clocksignal stets an alle Register (0 bis 3) weitergeleitet, ohne dass Vorbedingungen<br />

eine Rolle spielen. Im hier gezeigten Beispiel ist sichtbar, dass die Register 1 bis 3 kein<br />

12 Ein Programm zur Erzeugung der Gatternetzliste aus dem VHDL-Code.<br />

97