Abschlussbericht

Abschlussbericht

Abschlussbericht

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

weise ist, dass für jedes Feld und damit für jede Schlüssellänge eine spezielle Abbildung<br />

generiert werden muss. Hier ergibt sich das Problem der Reduktion: Entweder man hat<br />

eine schnelle, effiziente Implementierung, die aber nur eine bestimmte Kurve unterstützt<br />

oder einen komplexen Algorithmus, der dann aber nicht an bestimmte Kurven gebunden<br />

ist.<br />

In dem Design wurde sich auf die Beschleunigung einer einzigen Kurve konzentriert. Ziel<br />

war es, eine möglichst schnelle und kleine Hardwarelösung für die ECC-Operation mit<br />

einer Bitbreite von 233 Bit zu realisieren. Hierfür kann das Reduktionspolynom direkt in<br />

dem Design verdrahtet werden. Die Reduktionsoperation benötigt somit 0,034 mm 2 Siliziumfläche,<br />

während eine flexible Lösung die Fläche und auch die letztendliche Laufzeit<br />

signifikant erhöht hätten.<br />

Die Kurve mit Operanden von 233 Bit ist seitens der NIST unter der Bezeichnung „B 233“<br />

standardisiert [13]. Diese Kurve wurde ausgewählt, da die Sicherheit in etwa der Sicherheit<br />

des eingesetzten, symmetrischen Verschlüsselungsverfahren AES entspricht [6a].<br />

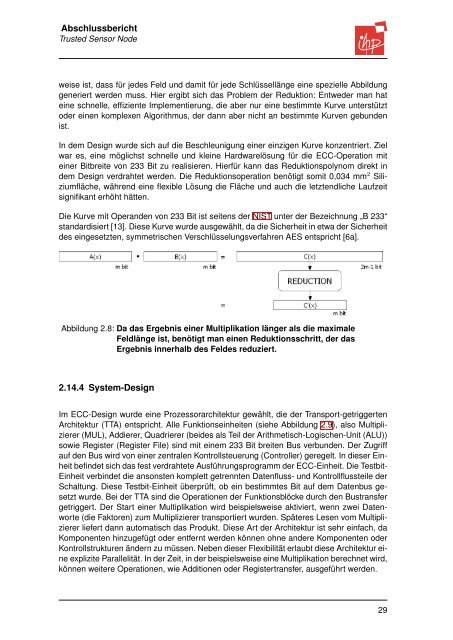

Abbildung 2.8: Da das Ergebnis einer Multiplikation länger als die maximale<br />

Feldlänge ist, benötigt man einen Reduktionsschritt, der das<br />

Ergebnis innerhalb des Feldes reduziert.<br />

2.14.4 System-Design<br />

Im ECC-Design wurde eine Prozessorarchitektur gewählt, die der Transport-getriggerten<br />

Architektur (TTA) entspricht. Alle Funktionseinheiten (siehe Abbildung 2.9), also Multiplizierer<br />

(MUL), Addierer, Quadrierer (beides als Teil der Arithmetisch-Logischen-Unit (ALU))<br />

sowie Register (Register File) sind mit einem 233 Bit breiten Bus verbunden. Der Zugriff<br />

auf den Bus wird von einer zentralen Kontrollsteuerung (Controller) geregelt. In dieser Einheit<br />

befindet sich das fest verdrahtete Ausführungsprogramm der ECC-Einheit. Die Testbit-<br />

Einheit verbindet die ansonsten komplett getrennten Datenfluss- und Kontrollflussteile der<br />

Schaltung. Diese Testbit-Einheit überprüft, ob ein bestimmtes Bit auf dem Datenbus gesetzt<br />

wurde. Bei der TTA sind die Operationen der Funktionsblöcke durch den Bustransfer<br />

getriggert. Der Start einer Multiplikation wird beispielsweise aktiviert, wenn zwei Datenworte<br />

(die Faktoren) zum Multiplizierer transportiert wurden. Späteres Lesen vom Multiplizierer<br />

liefert dann automatisch das Produkt. Diese Art der Architektur ist sehr einfach, da<br />

Komponenten hinzugefügt oder entfernt werden können ohne andere Komponenten oder<br />

Kontrollstrukturen ändern zu müssen. Neben dieser Flexibilität erlaubt diese Architektur eine<br />

explizite Parallelität. In der Zeit, in der beispielsweise eine Multiplikation berechnet wird,<br />

können weitere Operationen, wie Additionen oder Registertransfer, ausgeführt werden.<br />

29