Abschlussbericht

Abschlussbericht

Abschlussbericht

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Abschlussbericht</strong><br />

Trusted Sensor Node<br />

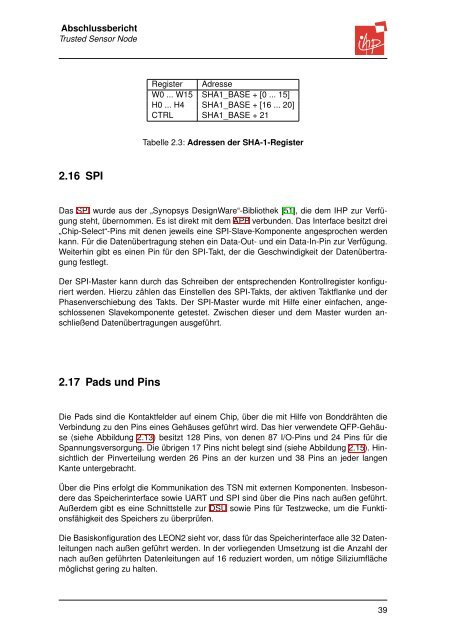

Register Adresse<br />

W0 ... W15 SHA1_BASE + [0 ... 15]<br />

H0 ... H4 SHA1_BASE + [16 ... 20]<br />

CTRL SHA1_BASE + 21<br />

Tabelle 2.3: Adressen der SHA-1-Register<br />

2.16 SPI<br />

Das SPI wurde aus der „Synopsys DesignWare“-Bibliothek [51], die dem IHP zur Verfügung<br />

steht, übernommen. Es ist direkt mit dem APB verbunden. Das Interface besitzt drei<br />

„Chip-Select“-Pins mit denen jeweils eine SPI-Slave-Komponente angesprochen werden<br />

kann. Für die Datenübertragung stehen ein Data-Out- und ein Data-In-Pin zur Verfügung.<br />

Weiterhin gibt es einen Pin für den SPI-Takt, der die Geschwindigkeit der Datenübertragung<br />

festlegt.<br />

Der SPI-Master kann durch das Schreiben der entsprechenden Kontrollregister konfiguriert<br />

werden. Hierzu zählen das Einstellen des SPI-Takts, der aktiven Taktflanke und der<br />

Phasenverschiebung des Takts. Der SPI-Master wurde mit Hilfe einer einfachen, angeschlossenen<br />

Slavekomponente getestet. Zwischen dieser und dem Master wurden anschließend<br />

Datenübertragungen ausgeführt.<br />

2.17 Pads und Pins<br />

Die Pads sind die Kontaktfelder auf einem Chip, über die mit Hilfe von Bonddrähten die<br />

Verbindung zu den Pins eines Gehäuses geführt wird. Das hier verwendete QFP-Gehäuse<br />

(siehe Abbildung 2.13) besitzt 128 Pins, von denen 87 I/O-Pins und 24 Pins für die<br />

Spannungsversorgung. Die übrigen 17 Pins nicht belegt sind (siehe Abbildung 2.15). Hinsichtlich<br />

der Pinverteilung werden 26 Pins an der kurzen und 38 Pins an jeder langen<br />

Kante untergebracht.<br />

Über die Pins erfolgt die Kommunikation des TSN mit externen Komponenten. Insbesondere<br />

das Speicherinterface sowie UART und SPI sind über die Pins nach außen geführt.<br />

Außerdem gibt es eine Schnittstelle zur DSU sowie Pins für Testzwecke, um die Funktionsfähigkeit<br />

des Speichers zu überprüfen.<br />

Die Basiskonfiguration des LEON2 sieht vor, dass für das Speicherinterface alle 32 Datenleitungen<br />

nach außen geführt werden. In der vorliegenden Umsetzung ist die Anzahl der<br />

nach außen geführten Datenleitungen auf 16 reduziert worden, um nötige Siliziumfläche<br />

möglichst gering zu halten.<br />

39