10-Gigabit Ethernet Switch Performance Testing - Ixia

10-Gigabit Ethernet Switch Performance Testing - Ixia

10-Gigabit Ethernet Switch Performance Testing - Ixia

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

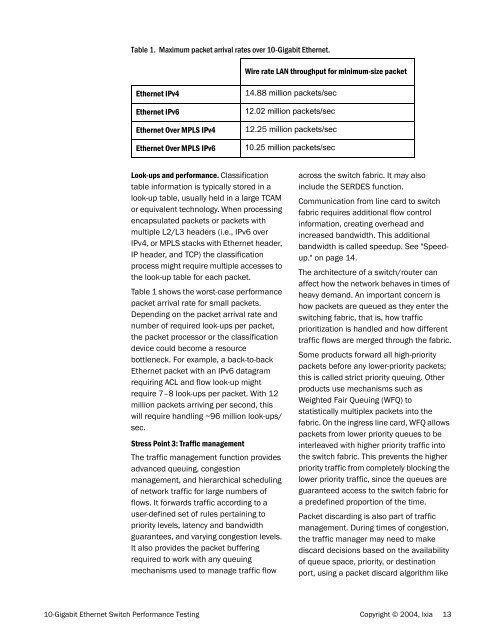

Table 1. Maximum packet arrival rates over <strong>10</strong>-<strong>Gigabit</strong> <strong>Ethernet</strong>.<br />

Look-ups and performance. Classification<br />

table information is typically stored in a<br />

look-up table, usually held in a large TCAM<br />

or equivalent technology. When processing<br />

encapsulated packets or packets with<br />

multiple L2/L3 headers (i.e., IPv6 over<br />

IPv4, or MPLS stacks with <strong>Ethernet</strong> header,<br />

IP header, and TCP) the classification<br />

process might require multiple accesses to<br />

the look-up table for each packet.<br />

Table 1 shows the worst-case performance<br />

packet arrival rate for small packets.<br />

Depending on the packet arrival rate and<br />

number of required look-ups per packet,<br />

the packet processor or the classification<br />

device could become a resource<br />

bottleneck. For example, a back-to-back<br />

<strong>Ethernet</strong> packet with an IPv6 datagram<br />

requiring ACL and flow look-up might<br />

require 7–8 look-ups per packet. With 12<br />

million packets arriving per second, this<br />

will require handling ~96 million look-ups/<br />

sec.<br />

Stress Point 3: Traffic management<br />

The traffic management function provides<br />

advanced queuing, congestion<br />

management, and hierarchical scheduling<br />

of network traffic for large numbers of<br />

flows. It forwards traffic according to a<br />

user-defined set of rules pertaining to<br />

priority levels, latency and bandwidth<br />

guarantees, and varying congestion levels.<br />

It also provides the packet buffering<br />

required to work with any queuing<br />

mechanisms used to manage traffic flow<br />

Wire rate LAN throughput for minimum-size packet<br />

<strong>Ethernet</strong> IPv4 14.88 million packets/sec<br />

<strong>Ethernet</strong> IPv6 12.02 million packets/sec<br />

<strong>Ethernet</strong> Over MPLS IPv4 12.25 million packets/sec<br />

<strong>Ethernet</strong> Over MPLS IPv6 <strong>10</strong>.25 million packets/sec<br />

across the switch fabric. It may also<br />

include the SERDES function.<br />

Communication from line card to switch<br />

fabric requires additional flow control<br />

information, creating overhead and<br />

increased bandwidth. This additional<br />

bandwidth is called speedup. See "Speedup."<br />

on page 14.<br />

The architecture of a switch/router can<br />

affect how the network behaves in times of<br />

heavy demand. An important concern is<br />

how packets are queued as they enter the<br />

switching fabric, that is, how traffic<br />

prioritization is handled and how different<br />

traffic flows are merged through the fabric.<br />

Some products forward all high-priority<br />

packets before any lower-priority packets;<br />

this is called strict priority queuing. Other<br />

products use mechanisms such as<br />

Weighted Fair Queuing (WFQ) to<br />

statistically multiplex packets into the<br />

fabric. On the ingress line card, WFQ allows<br />

packets from lower priority queues to be<br />

interleaved with higher priority traffic into<br />

the switch fabric. This prevents the higher<br />

priority traffic from completely blocking the<br />

lower priority traffic, since the queues are<br />

guaranteed access to the switch fabric for<br />

a predefined proportion of the time.<br />

Packet discarding is also part of traffic<br />

management. During times of congestion,<br />

the traffic manager may need to make<br />

discard decisions based on the availability<br />

of queue space, priority, or destination<br />

port, using a packet discard algorithm like<br />

<strong>10</strong>-<strong>Gigabit</strong> <strong>Ethernet</strong> <strong>Switch</strong> <strong>Performance</strong> <strong>Testing</strong> Copyright © 2004, <strong>Ixia</strong> 13