BajaPPC-750 User's Manual - Emerson Network Power

BajaPPC-750 User's Manual - Emerson Network Power

BajaPPC-750 User's Manual - Emerson Network Power

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

3-8 <strong>BajaPPC</strong>-<strong>750</strong>: Central Processing Unit<br />

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15<br />

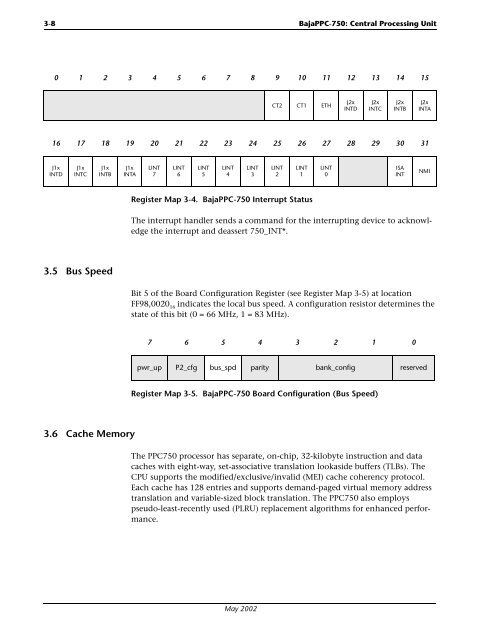

3.5 Bus Speed<br />

3.6 Cache Memory<br />

The interrupt handler sends a command for the interrupting device to acknowledge<br />

the interrupt and deassert <strong>750</strong>_INT*.<br />

Bit 5 of the Board Configuration Register (see Register Map 3-5) at location<br />

FF98,0020 16 indicates the local bus speed. A configuration resistor determines the<br />

state of this bit (0 = 66 MHz, 1 = 83 MHz).<br />

The PPC<strong>750</strong> processor has separate, on-chip, 32-kilobyte instruction and data<br />

caches with eight-way, set-associative translation lookaside buffers (TLBs). The<br />

CPU supports the modified/exclusive/invalid (MEI) cache coherency protocol.<br />

Each cache has 128 entries and supports demand-paged virtual memory address<br />

translation and variable-sized block translation. The PPC<strong>750</strong> also employs<br />

pseudo-least-recently used (PLRU) replacement algorithms for enhanced performance.<br />

May 2002<br />

CT2 CT1 ETH<br />

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31<br />

J1x<br />

INTD<br />

J1x<br />

INTC<br />

J1x<br />

INTB<br />

J1x<br />

INTA<br />

LINT<br />

7<br />

LINT<br />

6<br />

LINT<br />

5<br />

LINT<br />

4<br />

LINT<br />

3<br />

LINT<br />

2<br />

LINT<br />

1<br />

Register Map 3-4. <strong>BajaPPC</strong>-<strong>750</strong> Interrupt Status<br />

LINT<br />

0<br />

J2x<br />

INTD<br />

J2x<br />

INTC<br />

J2x<br />

INTB<br />

7 6 5 4 3 2 1 0<br />

pwr_up P2_cfg bus_spd parity bank_config reserved<br />

Register Map 3-5. <strong>BajaPPC</strong>-<strong>750</strong> Board Configuration (Bus Speed)<br />

ISA<br />

INT<br />

J2x<br />

INTA<br />

NMI