FM3 MB9B500 Series - Microcontrollers - Fujitsu

FM3 MB9B500 Series - Microcontrollers - Fujitsu

FM3 MB9B500 Series - Microcontrollers - Fujitsu

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>MB9B500</strong> <strong>Series</strong><br />

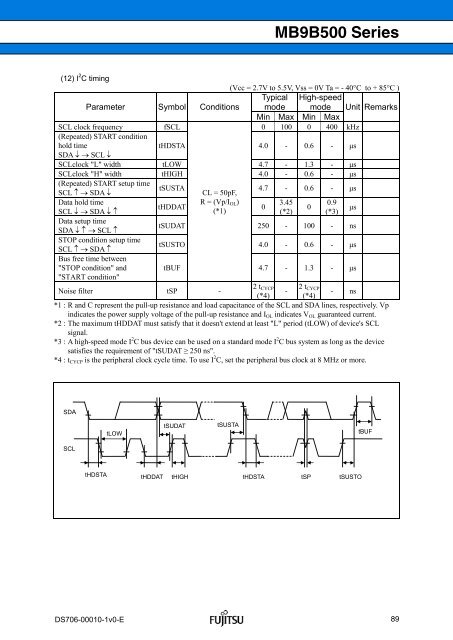

(12) I 2 C timing<br />

(Vcc = 2.7V to 5.5V, Vss = 0V Ta = - 40C to + 85C)<br />

Typical High-speed<br />

Parameter Symbol Conditions mode mode Unit Remarks<br />

Min Max Min Max<br />

SCL clock frequency<br />

(Repeated) START condition<br />

fSCL 0 100 0 400 kHz<br />

hold time<br />

SDA SCL <br />

tHDSTA 4.0 - 0.6 - μs<br />

SCLclock "L" width tLOW 4.7 - 1.3 - μs<br />

SCLclock "H" width tHIGH 4.0 - 0.6 - μs<br />

(Repeated) START setup time<br />

SCL SDA <br />

tSUSTA<br />

CL = 50pF,<br />

4.7 - 0.6 - μs<br />

Data hold time<br />

SCL SDA <br />

tHDDAT<br />

R = (Vp/IOL)<br />

(*1)<br />

0<br />

3.45<br />

(*2)<br />

0<br />

0.9<br />

(*3)<br />

μs<br />

Data setup time<br />

SDA SCL <br />

tSUDAT 250 - 100 - ns<br />

STOP condition setup time<br />

SCL SDA <br />

Bus free time between<br />

tSUSTO 4.0 - 0.6 - μs<br />

"STOP condition" and<br />

"START condition"<br />

tBUF<br />

4.7 - 1.3 - μs<br />

2 tCYCP<br />

2 tCYCP<br />

Noise filter tSP -<br />

-<br />

- ns<br />

(*4) (*4)<br />

*1 : R and C represent the pull-up resistance and load capacitance of the SCL and SDA lines, respectively. Vp<br />

indicates the power supply voltage of the pull-up resistance and IOL indicates VOL guaranteed current.<br />

*2 : The maximum tHDDAT must satisfy that it doesn't extend at least "L" period (tLOW) of device's SCL<br />

signal.<br />

*3 : A high-speed mode I 2 C bus device can be used on a standard mode I 2 C bus system as long as the device<br />

satisfies the requirement of "tSUDAT ≥ 250 ns".<br />

*4 : tCYCP is the peripheral clock cycle time. To use I 2 C, set the peripheral bus clock at 8 MHz or more.<br />

SDA<br />

SCL<br />

tHDSTA<br />

tLOW<br />

DS706-00010-1v0-E<br />

tHDDAT<br />

tSUDAT<br />

tHIGH<br />

tSUSTA<br />

tHDSTA tSP<br />

tSUSTO<br />

tBUF<br />

89