Robust System Design - VLSI

Robust System Design - VLSI

Robust System Design - VLSI

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

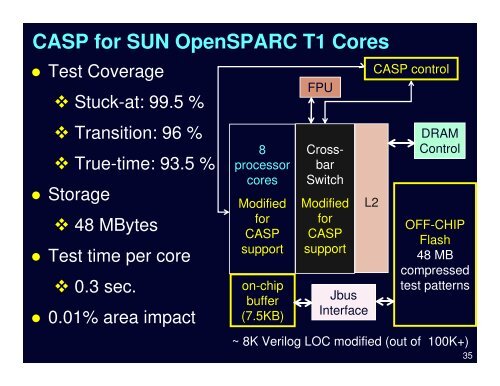

CASP for SUN OpenSPARC T1 Cores<br />

Test Coverage<br />

Stuck-at: 99.5 %<br />

Transition: 96 %<br />

True-time: 93.5 %<br />

Storage<br />

48 MBytes<br />

Test time per core<br />

0.3 sec.<br />

0.01% area impact<br />

8<br />

processor<br />

cores<br />

Modified<br />

for<br />

CASP<br />

support<br />

on-chip<br />

buffer<br />

(7.5KB)<br />

FPU<br />

Crossbar<br />

Switch<br />

Modified<br />

for<br />

CASP<br />

support<br />

Jbus<br />

Interface<br />

L2<br />

CASP control<br />

DRAM<br />

Control<br />

OFF-CHIP<br />

Flash<br />

48 MB<br />

compressed<br />

test patterns<br />

~ 8K Verilog LOC modified (out of 100K+)<br />

35