- Page 2 and 3: LITERATURE To order Intel Literatur

- Page 4 and 5: INTERNATIONAL LITERATURE ORDER FORM

- Page 6 and 7: inter Intel Corporation makes no wa

- Page 9 and 10: Table of Contents CHAPTER 1 INTRODU

- Page 11 and 12: Table of Contents (continued) 8.1.2

- Page 13: Table of Contents (continued) APPEN

- Page 17 and 18: CHAPTER 1 INTRODUCTION The 80C 186E

- Page 19 and 20: INTRODUCTION Some customers may not

- Page 21: INTRODUCTION 80C186EB: This refers

- Page 25 and 26: CHAPTER 2 OVERVIEW OF THE 80C186 FA

- Page 27 and 28: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 29 and 30: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 31 and 32: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 33 and 34: inter OVERVIEW OF THE 80C186 FAMILY

- Page 35 and 36: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 37 and 38: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 39 and 40: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 41 and 42: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 43: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 47 and 48: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 49 and 50: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 51 and 52: OVERVIEW OF THE 80C186 FAMILY MODUL

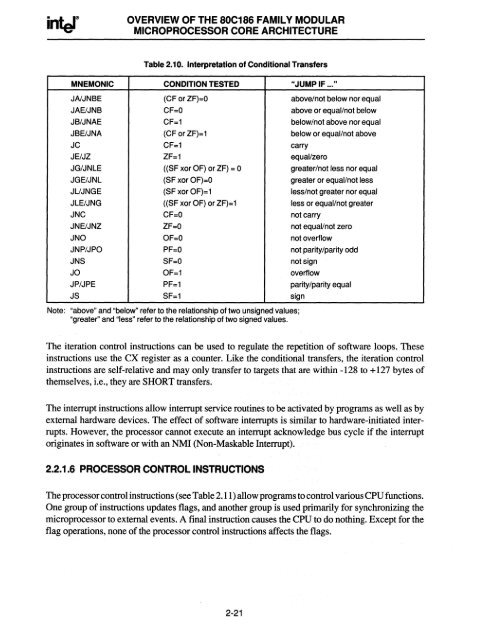

- Page 53 and 54: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 55 and 56: OVERVIEW OF THE 80C186 FAMILY MODUL

- Page 57: Bus Interface Unit 3

- Page 60 and 61: BUS INTERFACE UNIT '--lm I T. I~ I

- Page 62 and 63: BUS INTERFACE UNIT 3.2 PHYSICAL ADD

- Page 64 and 65: BUS INTERFACE UNIT Non-pipelinedEA

- Page 66 and 67: BUS INTERFACE UNIT Any 80C 188 Core

- Page 68 and 69: BUS INTERFACE UNIT LATCH ALE ~ READ

- Page 70 and 71: BUS INTERFACE UNIT 3.4.3.1 TEST INP

- Page 72 and 73: BUS INTERFACE UNIT CPU·DERIVED SIG

- Page 74 and 75: BUS INTERFACE UNIT CLOCK OUT READY

- Page 76 and 77: BUS INTERFACE UNIT 80C186 MODULAR C

- Page 78 and 79: BUS INTERFACE UNIT 3.7.3 WAIT STATE

- Page 80 and 81: BUS INTERFACE UNIT 1II0V mov out mo

- Page 82 and 83: BUS INTERFACE UNIT 3.8.2 HOLD/HLDA

- Page 84 and 85: BUS INTERFACE UNIT T,OR Tw T, CLOCK

- Page 86 and 87: BUS INTERFACE UNIT A special mechan

- Page 89 and 90: CHAPTER 4 CLOCK GENERATOR The clock

- Page 91 and 92: CLOCK GENERATOR The RC tank circuit

- Page 93 and 94: CLOCK GENERATOR ClKIN 1 1 1 1 Vee 1

- Page 95:

CLOCK GENERATOR ClKIN RESIN RESYNC

- Page 99 and 100:

CHAPTERS PERIPHERAL CONTROL BLOCK A

- Page 101 and 102:

PERIPHERAL CONTROL BLOCK All commun

- Page 103:

inter PERIPHERAL CONTROL BLOCK 5.3

- Page 107 and 108:

CHAPTER 6 TIMER / COUNTER UNIT The

- Page 109 and 110:

TIMER/COUNTER UNIT TIMER 0 and TIME

- Page 111 and 112:

TIMER/COUNTER UNIT TIMER 1 TIMER 2

- Page 113 and 114:

inter TIMER/COUNTER UNIT YES NO YES

- Page 115 and 116:

TIMER/COUNTER UNIT 6.2 TIMER EVENTS

- Page 117 and 118:

TIMER/COUNTER UNIT When the timer i

- Page 119 and 120:

TIMER/COUNTER UNIT the write, the E

- Page 121 and 122:

TIMER/COUNTER UNIT bump_minute: mov

- Page 123:

TIMER/COUNTER UNIT set_count code x

- Page 127 and 128:

CHAPTER 7 CHIP SELECT/READY LOGIC U

- Page 129 and 130:

CHIP SELECT/READY LOGIC UNIT The Ch

- Page 131 and 132:

CHIP SELECT/READY LOGIC UNIT CHIP S

- Page 133 and 134:

CHIP SELECT/READY LOGIC UNIT Case 1

- Page 135 and 136:

CHIP SELECT/READY LOGIC UNIT EXAMPL

- Page 137 and 138:

CHIP SELECT/READY LOGIC UNIT READY

- Page 139 and 140:

inter CHIP SELECT/READY LOGIC UNIT

- Page 141 and 142:

CHIP SELECT/READY LOGIC UNIT 7.4 AP

- Page 143 and 144:

CHIP SELECT/READY LOGIC UNIT Exampl

- Page 145 and 146:

CHIP SELECT/READY LOGIC UNIT The fi

- Page 147 and 148:

inter CHIP SELECT/READY LOGIC UNIT

- Page 149:

intJ CHIP SELECT/READY LOGIC UNIT m

- Page 153:

CHAPTER 8 SERIAL COMMUNICATIONS UNI

- Page 156 and 157:

SERIAL COMMUNICATIONS UNIT BAUD RAT

- Page 158 and 159:

S&RIAl1.COMMUNICATIONS·UNIT SERIAL

- Page 160 and 161:

SERIAL COMMUNICATIONS UNIT 8.1.1.1

- Page 162 and 163:

SERIAL COMMUNICATIONS UNIT 8.1.1.2

- Page 164 and 165:

SERIAL COMMUNICATIONS UNIT 8.1.1.3

- Page 166 and 167:

SERIAL COMMUNICATIONS UNIT Initiall

- Page 168 and 169:

SERIAL COMMUNICATIONS UNIT Received

- Page 170 and 171:

SERIAL COMMUNICATIONS UNIT REN Bit:

- Page 172 and 173:

SERIAL COMMUNICATIONS UNIT The foll

- Page 174 and 175:

SERIAL COMMUNICATIONS UNIT CLKOUT T

- Page 176 and 177:

SERIAL COMMUNICATIONS UNIT CTS SAMP

- Page 178 and 179:

SERIAL COMMUNICATIONS UNIT At the i

- Page 180 and 181:

SERIAL COMMUNICATIONS UNIT Example

- Page 182 and 183:

SERIAL COMMUNICATIONS UNIT Example

- Page 184 and 185:

SERIAL COMMUNICATIONS UNIT Example

- Page 187 and 188:

CHAPTER 9 INTERRUPTS 80C186EB famil

- Page 189 and 190:

intJ INTERRUPTS interrupted by high

- Page 191 and 192:

INTERRUPTS Interrupt on Overflow·

- Page 193 and 194:

INTERRUPTS 9.3.1 INTERRUPT LATENCY

- Page 195 and 196:

INTERRUPTS interrupt service routin

- Page 197 and 198:

INTERRUPTS 9.4 INTERRUPT CONTROL UN

- Page 199 and 200:

INTERRUPTS 9.4.2 INTERRUPT UNIT PRO

- Page 201 and 202:

INTERRUPTS INTERRUPT CONTROL REGIST

- Page 203 and 204:

INTERRUPTS 9.4.2.4 THE REQUEST REGI

- Page 205 and 206:

inter INTERRUPTS 9.4.2.6 THE PRIORI

- Page 207 and 208:

INTERRUPTS POLL AND POLL STATUS REG

- Page 209 and 210:

INTERRUPTS INTERRUPT STATUS REGISTE

- Page 211 and 212:

INTERRUPTS When the integrated Inte

- Page 213 and 214:

INTERRUPTS 9.4.4.3 INTERRUPT RESPON

- Page 215 and 216:

INTERRUPTS YES PRESENT INTERRUPT RE

- Page 217:

Refresh Control Unit 10

- Page 220 and 221:

intJ REFRESH CONTROL UNIT 10.1 REFR

- Page 222 and 223:

inter REF.RESH CONTROL UNIT REFRESH

- Page 224 and 225:

inl:el® REFRESH CONTROL UNIT REFRE

- Page 226 and 227:

REFRESH CONTROL UNIT TI T1 TI T1 T1

- Page 229:

Input/Output Port Unit 11

- Page 232 and 233:

INPUT/OUTPUT PORT UNIT F·BUS GCS7

- Page 234 and 235:

INPUT/OUTPUT PORT UNIT PORT 1 DIREC

- Page 236 and 237:

inter INPUT/OUTPUTPORT UNIT PORT 2

- Page 238 and 239:

INPUT/OUTPUT PORT UNIT FROM INTEGRA

- Page 240 and 241:

inter INPUT/OUTPUT PORT UNIT READ P

- Page 242 and 243:

INPUT/OUTPUT PORT UNIT PORT DIRECTI

- Page 244 and 245:

INPUTJOUTPUTPORT UNIT 11.4 PROGRAMM

- Page 247 and 248:

CHAPTER 12 POWER MANAGEMENT UNIT Th

- Page 249 and 250:

POWER MANAGEMENT UNIT 12.1 FUNCTION

- Page 251 and 252:

l .. "11 Ti Ti cO r:: CiJ I CLKOUT

- Page 253 and 254:

POWER MANAGEMENT UNIT 12.1.1.3 EXIT

- Page 255 and 256:

( ::!! cc c iii ... ~ i:» m ~. d:

- Page 257 and 258:

POWER MANAGEMENT UNIT PDTMR PIN r--

- Page 259 and 260:

O~: _______________________________

- Page 261:

POWER MANAGEMENT UNIT Example 1. ho

- Page 265 and 266:

CHAPTER 13 HARDWARE PROVISIONS FOR

- Page 267 and 268:

HARDWARE PROVISIONS FOR FLOATING PO

- Page 269 and 270:

HARDWARE PROVISIONS FOR FLOATING PO

- Page 271 and 272:

HARDWARE PROVISIONS FOR FLOATING PO

- Page 273:

ONCE Mode 14

- Page 277:

Differences Between the 80C 186 Fam

- Page 280 and 281:

APPENDIX A A.4 HOLD/HLDA VS. REQUES

- Page 282 and 283:

APPENDIX A INTERRUPTED STRING MOVE

- Page 285 and 286:

APPENDIX B SUMMARY OF DIFFERENCES B

- Page 287 and 288:

APPENDIX B B.1.2 SEMICONDUCTOR TECH

- Page 289 and 290:

APPENDIXB B.4INTERRUPT CONTROLLER T

- Page 291:

Differences Between 80C186EB and 80

- Page 295:

Synchronization Appendix 0

- Page 298 and 299:

APPENDIX 0 Thus, the output of this

- Page 301 and 302:

APPENDIXE Appendix E. Instruction S

- Page 303 and 304:

APPENDIX E Appendix E. Instruction

- Page 305 and 306:

APPENDIXE Appendix E. Instruction S

- Page 307 and 308:

Instruction Summary 2 AppendixF

- Page 309 and 310:

APPENDIX F 1ST BYTE HEX Appendix F.

- Page 311 and 312:

APPENDIXF 1ST BYTE HEX BINARY Appen

- Page 313 and 314:

APPENDIXF Appendix F. Machine Instr

- Page 315 and 316:

APPENDIX F 1ST BYTE HEX BINARY Appe

- Page 317:

APPENDIX F 1ST BYTE HEX BINARY Appe

- Page 321:

APPENDIXG LO HI 0 1 2 3 0 ADD ADD A

- Page 325 and 326:

APPENDIXH MODAL PIN STATES The tenn

- Page 327 and 328:

APPENDIX H Name Modal State Type De

- Page 329:

APPENDIXH Name Modal State Type Des

- Page 333 and 334:

inter ALABAMA ~~I ~:llord Dr .. #2

- Page 335 and 336:

intel~ DOMESTIC DISTRIBUTORS (Contd

- Page 337 and 338:

INTERNATIONAL SALES OFFICES AUSTRAL

- Page 340:

UNITED STATES Intel Corporation 306