- Page 1 and 2: DATA 620/i SYSTEM REFERENCE MANUAL

- Page 3 and 4: VDM-3000 Revision A March 1968

- Page 5 and 6: Page SECTION 5 CONTROL CONSOLE OPER

- Page 7 and 8: The unique design of the DA TA 620/

- Page 9 and 10: Table 1-1. (Continued) Specifi cati

- Page 11 and 12: Table 1-1. (Continued) Specifi cati

- Page 13 and 14: Detailed design and maintenance inf

- Page 15 and 16: SET R., SET U'" J POI 26801A R REGI

- Page 17 and 18: A register. This full-length regist

- Page 19 and 20: made available on an external cable

- Page 21 and 22: 17 16 15 14 13 12 11 10 9 8 7 6 5 4

- Page 23 and 24: n 17 16 15 14 13 12 11 10 9 8 7 6 5

- Page 25 and 26: 620/i -01 Memory /Periphera I Contr

- Page 27 and 28: un ique memory destination address

- Page 29 and 30: Table G-1 (d), appendix G, summariz

- Page 31 and 32: P0131802A BRING INSTRUCTION (W-+U)

- Page 33: Relative: Yes Indexing: Yes Indirec

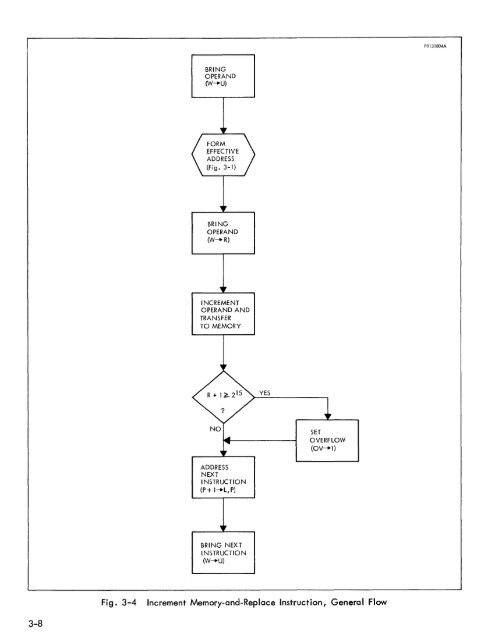

- Page 37 and 38: I ncrement Memory and Replace Timin

- Page 39 and 40: The contents of the A and B registe

- Page 41 and 42: ANA AND Memory and A Timing: 2 cycl

- Page 43 and 44: The overflow indicator (OF) is set.

- Page 45 and 46: Indexing: No Indirect Addressing: N

- Page 47 and 48: LLRL Long Logical Rotate Left Timin

- Page 49 and 50: I ASLB I Arithmetic Shift B Left Ti

- Page 51 and 52: 15 14 13 12 11 10 9 8 7 6 5 4 3 2 0

- Page 53 and 54: The contents of the A (B, X) regist

- Page 55 and 56: Indexing: No Indirect Addressing: N

- Page 57 and 58: A¢FB Add Overflow to B Register Ti

- Page 59 and 60: P0131807A r------, 1 BRING I : INST

- Page 61 and 62: POJ3J808A BRING INSTRUCTION (W-+U)

- Page 63 and 64: ~ Jump if A Register Zero Timing: 2

- Page 65 and 66: ~ Jump if Sense Switch 3 Set Timing

- Page 67 and 68: Indexing: No Indirect Addressing: Y

- Page 69 and 70: JBZM Jump and Mark if B Register Ze

- Page 71 and 72: Execute instru'ction group. For the

- Page 73 and 74: X¢F Execute if Overflow Set Timing

- Page 75 and 76: §] Execute it' B Regi ster Timing:

- Page 77 and 78: Extended-addressing instruction gro

- Page 79 and 80: STAE Store A Reg i ster Extended Ti

- Page 81 and 82: ADDE Add Memory to A Timing: 3 cycl

- Page 83 and 84: If (A,B) ~1 --;::x- (divisor> divid

- Page 85 and 86:

ANAE AND Memory and A Timing: 3 cyc

- Page 87 and 88:

LDXI Load X Reg i ste r Immediate T

- Page 89 and 90:

I ADDI I Add Immediate Timing: 2 cy

- Page 91 and 92:

(divisor> dividend, taken as a bina

- Page 93 and 94:

ANAl AND Immediate Timing: 2 cycles

- Page 95 and 96:

P0131811A A~ I L-BUS 1 r-J---, r-J-

- Page 97 and 98:

Table 4-1. I/O-Cable Control Line S

- Page 99 and 100:

P0131812A BRING INSTRUCTION (W-'U)

- Page 101 and 102:

~ Clear and Input to B Register Tim

- Page 103 and 104:

~ I o P0131813A BRING INSTRUCTION r

- Page 105 and 106:

. A trap timing sequence is initiat

- Page 107 and 108:

4.4.2 Program Interrupt (optional)

- Page 109 and 110:

P0131815A DATA-.:aO/i Fig. 5-1 Cont

- Page 111 and 112:

Table 5-1. (Continued) Control or I

- Page 113 and 114:

APPENDICES

- Page 115 and 116:

DATA 620/i Number System Binary num

- Page 117 and 118:

The negative result is in error. Th

- Page 119 and 120:

~ Standard DATA 620/i Subroutines I

- Page 121 and 122:

Appendix C Table of Powers of Two

- Page 123 and 124:

Appendix D Octal-Decimal Integer Co

- Page 125 and 126:

Octal-Decimal Integer Conversion Ta

- Page 127 and 128:

Octal-Decimal Integer Conversion Ta

- Page 129 and 130:

Octal-Decimal Fraction Conversion T

- Page 131 and 132:

Octal-DecImal Fraction Conversion T

- Page 133 and 134:

Appendix F DATA 620/i Instructions

- Page 135 and 136:

WDS/ Time Indirect I Mnemonic Octal

- Page 137 and 138:

Mnemonic Octal Description WDS/ Tim

- Page 139 and 140:

Appendix G DATA 620/i Instructions

- Page 141 and 142:

Table G-1 (c) Logical Instruction G

- Page 143 and 144:

Table G-3(b) Instruction Format Us

- Page 145 and 146:

Table G-5 Jump Instruction Group Ta

- Page 147 and 148:

Table G-7 Execute Instruction Group

- Page 149 and 150:

Table G-11 Input/Output Instruction

- Page 151 and 152:

Appendix H DA TA 620/i Reserved Ins

- Page 153 and 154:

Table H-2 BIC Reserved Instruction

- Page 155 and 156:

Table H-3(b) Model B Teletype Instr

- Page 157 and 158:

Table H-5 Gated-Input-Channel Reser

- Page 159 and 160:

Table H-7 Gated-Output-Channel Rese

- Page 161 and 162:

Table H-10 Magnetic Tape Unit Reser

- Page 163 and 164:

Appendix I DATA 620/i Standard BCD

- Page 165 and 166:

DATA 620/i Standard BCD Codes (cont

- Page 167:

Teletype Character Codes (continued