DATA 620/i SYSTEM REFERENCE MANUAL . - Al Kossow's Bitsavers

DATA 620/i SYSTEM REFERENCE MANUAL . - Al Kossow's Bitsavers

DATA 620/i SYSTEM REFERENCE MANUAL . - Al Kossow's Bitsavers

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

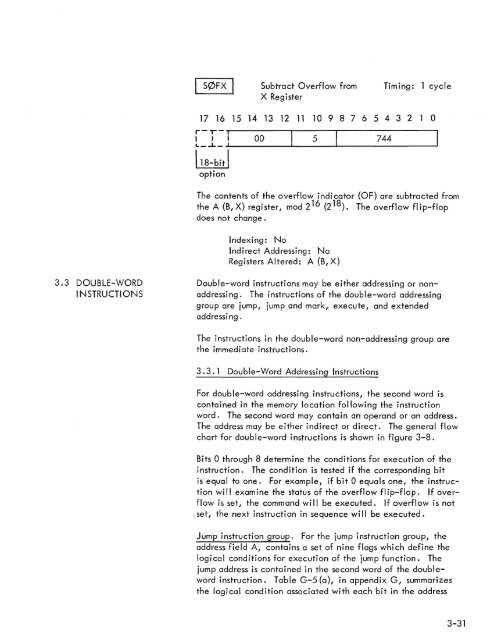

S¢FX<br />

Subtract Overflow from<br />

X Register<br />

Timing: 1 cycle<br />

17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 0<br />

f-T- !<br />

L _ -L _ ..L. ______<br />

IIS-bitl<br />

option<br />

00 5 744<br />

...L.....___--I-_________----"'<br />

The contents of the overflow indi cator (OF) are subtracted from<br />

the A (B,X) register, mod 2 16 (2 18 ). The overflow flip-flop<br />

does not change.<br />

Indexing: No<br />

Indirect Addressing: No<br />

Registers <strong>Al</strong>tered: A (B, X)<br />

3.3 DOUBLE-WORD<br />

INSTRUCTIONS<br />

Double-word instructions may be either addressing or nonaddressing.<br />

The instructions of the double-word addressing<br />

group are jump, jump and mark, execute, and extended<br />

addressing.<br />

The instructions. in the double-word non-addressing group are<br />

the immediate instructions.<br />

3.3. 1 Double-Word Addressing Instructions<br />

For double-word addressing instructions, the second word is<br />

contained in the memory location following the instruction<br />

word. The second word may contain an operand or an address.<br />

The address may be either indirect or direct. The general flow<br />

chart for double-word instructions is shown in figure 3-8.<br />

Bits 0 through 8 determine the conditions for execution of the<br />

instruction. The condition is tested if the corresponding bit<br />

is equal to one. For example, if bit 0 equals one, the instruction<br />

wi II exam ine the status of the overflow fl ip-flop. If overflow<br />

is set, the command wi" be executed. If overflow is not<br />

set, the next instruction in sequence will be executed.<br />

Jump instruction group. For the jump instruction group, the<br />

address field A, contains a set of nine flags which define the<br />

logical conditions for execution of the jump function. The<br />

jump address is contained in the second word of the doubleword<br />

instruction. Table G-5 (a), in appendix G, summarizes<br />

the logical condition associated with each bit in the address<br />

3-31