DATA 620/i SYSTEM REFERENCE MANUAL . - Al Kossow's Bitsavers

DATA 620/i SYSTEM REFERENCE MANUAL . - Al Kossow's Bitsavers

DATA 620/i SYSTEM REFERENCE MANUAL . - Al Kossow's Bitsavers

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

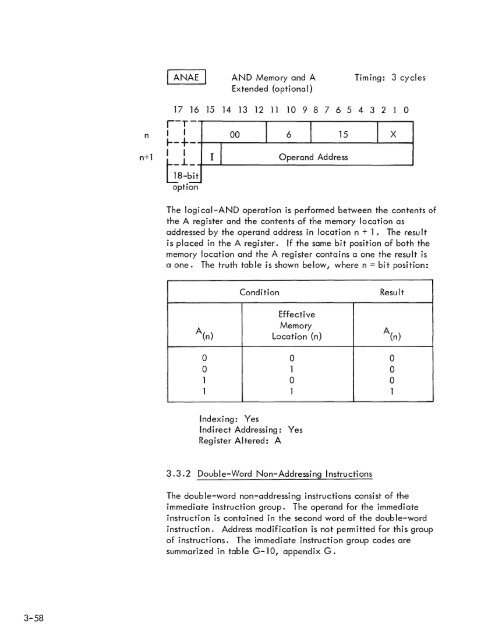

ANAE AND Memory and A Timing: 3 cycles<br />

Extended (opti ona I)<br />

n<br />

n+1<br />

17 16 15 14 13 12 11 10 9 8 7 6 5 432 1 0<br />

r-r-<br />

I I 00 6 15 X<br />

~-+ti<br />

I<br />

l I<br />

l8-bit -<br />

option<br />

I<br />

Operand Address<br />

The logi cal-AND operation is performed between the contents of<br />

the A register and the contents of the memory location as<br />

addressed by the operand address in location n + 1. The resu It<br />

is placed in the A register. If the same bit position of both the<br />

memory location and the A register contains a one the result is<br />

a one. The truth table is shown below, where n = bit position:<br />

A(n)<br />

Condition<br />

Effective<br />

Memory<br />

Location (n)<br />

Result<br />

A(n)<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

0<br />

0<br />

0<br />

1<br />

Indexing: Yes<br />

Indirect Addressing: Yes<br />

Register <strong>Al</strong>tered: A<br />

3.3.2 Double-Word Non-Addressing Instructions<br />

The double-word non-addressing instructions consist of the<br />

immediate instruction group. The operand for the immediate<br />

instruction is contained in the second word of the double-word<br />

instruction. Address modification is not permitted for this group<br />

of instructions. The immediate instruction group codes are<br />

summarized in table G-10, appendix G.<br />

3-58