- Page 5 and 6: 4.3.8 Message Class ...............

- Page 7 and 8: 5.11.4.2 Flow Control Update DLLP T

- Page 9 and 10: 9.7 Thermal Sensor.................

- Page 11 and 12: 16.2 Intel® VT-d..................

- Page 13 and 14: 19.5.7.15LMMIOL.BASE: Local MMIOL B

- Page 15 and 16: 19.7.1.16QPIP[1:0]NFERRST: Intel Qu

- Page 17 and 18: 19.10.2.15QPIPSUBSAD: Intel QuickPa

- Page 19 and 20: 19.11.5.15ACSCAPHDR: Access Control

- Page 21 and 22: 12-1 Example of Intel ME Configurat

- Page 23 and 24: 11-2 System and ESI Link Power Stat

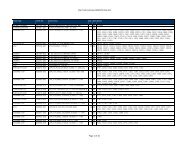

- Page 25 and 26: 20-34 IOH Signals (by Signal Name)

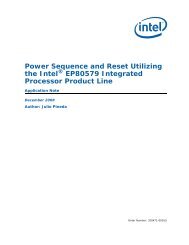

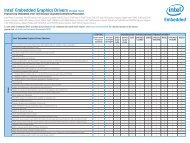

- Page 27 and 28: Product FeaturesProcessor Supports

- Page 29 and 30: 1 IntroductionThe Intel ® 5520 Chi

- Page 31 and 32: 1.1 Feature SummaryThe IOH provides

- Page 33 and 34: x8 Server I/O Module (SIOM) support

- Page 35 and 36: Table 1-2. Terminology (Sheet 2 of

- Page 37 and 38: Table 1-3.Related DocumentsDocument

- Page 39 and 40: 2 Platform Topology2.1 Introduction

- Page 41 and 42: Figure 2-3.Example: Intel Xeon 5500

- Page 43 and 44: 3 Interfaces3.1 IntroductionThis ch

- Page 45 and 46: 3.2.1.4 ClockingThe Intel QuickPath

- Page 47 and 48: Table 3-2. Protocol Transactions Su

- Page 49 and 50: Figure 3-2.Intel 5520 Chipset PCI E

- Page 51 and 52: 3.3.5.2 Isochronous Support and Vir

- Page 53 and 54:

The IOH ESI interface supports feat

- Page 55 and 56:

Sequencing these commands initiates

- Page 57 and 58:

Table 3-7.Memory Region Address Fie

- Page 59 and 60:

3.7.7.1 SMBus Configuration and Mem

- Page 61 and 62:

3.7.7.3 SMBus Configuration and Mem

- Page 63 and 64:

3.7.7.6 SMBus Configuration and Mem

- Page 65 and 66:

If a memory region address field is

- Page 67 and 68:

4 Intel ® QuickPath Interconnect4.

- Page 69 and 70:

Table 4-1.Link Layer Parameter Valu

- Page 71 and 72:

4.3.7.1 Link Level RetryLink level

- Page 73 and 74:

4.4.1.4 Dual IOH ProxyIn this mode

- Page 75 and 76:

Table 4-3.Slave to Master Conflict

- Page 77 and 78:

Table 4-5.Memory Address Decoder Fi

- Page 79 and 80:

4.5.5.2 RdCodePeerAgents list compr

- Page 81 and 82:

4.5.6.2 Lock ArbiterStopReq1&2 and

- Page 83 and 84:

Table 4-10. Protocol Transactions S

- Page 85 and 86:

4.8 Write CacheThe IOH write cache

- Page 87 and 88:

4.10 Conflict HandlingA coherent co

- Page 89 and 90:

The AckCnflt phase is completed by

- Page 91 and 92:

5 PCI Express and ESI Interfaces5.1

- Page 93 and 94:

Table 5-1.Supported Degraded ModesO

- Page 95 and 96:

5.3.4.1 Read Completion CombiningTh

- Page 97 and 98:

Table 5-4.Incoming PCI Express Memo

- Page 99 and 100:

5.4.3.1 ASSERT_GPE / DEASSERT_GPEUp

- Page 101 and 102:

5.7.1 Transaction IDThe Transaction

- Page 103 and 104:

5.9 Miscellaneous5.9.1 Number of Ou

- Page 105 and 106:

5.11.2 Link Level RetryThe PCI Expr

- Page 107 and 108:

Table 5-12. PCI Express Credit Mapp

- Page 109 and 110:

Table 5-14. Outgoing ESI Messages (

- Page 111 and 112:

Table 5-15.ESI Transaction ID Handl

- Page 113 and 114:

6 Ordering6.1 IntroductionThe IOH s

- Page 115 and 116:

Rule 9.If an inbound read completes

- Page 117 and 118:

6.3.3 Local Peer-to-PeerLocal peer-

- Page 119 and 120:

7 System Address MapThis chapter pr

- Page 121 and 122:

7.1.1 System DRAM Memory RegionsAdd

- Page 123 and 124:

7.1.3 Address Region Between 1 MB a

- Page 125 and 126:

This is a 1 MB range used to map I/

- Page 127 and 128:

(unless modified via the NS attribu

- Page 129 and 130:

7.3.1 PCI Express Configuration Spa

- Page 131 and 132:

For positive decoding, the memory d

- Page 133 and 134:

Table 7-3.Subtractive Decoding of O

- Page 135 and 136:

Table 7-4.Inbound Memory Address De

- Page 137 and 138:

7.6 Intel ® VT-d Address Map Impli

- Page 139 and 140:

8 Interrupts8.1 OverviewThe IOH sup

- Page 141 and 142:

Figure 8-1.Legacy Interrupt Routing

- Page 143 and 144:

Table 8-2. I/OxAPIC Table Mapping t

- Page 145 and 146:

egarding the interrupt destination

- Page 147 and 148:

Requester ID, that is, the IOH need

- Page 149 and 150:

8.3.2.1 Legacy Logical Mode Interru

- Page 151 and 152:

needs to check for local/remote rou

- Page 153 and 154:

FECx_xxxx in the IOH. The IOH provi

- Page 155 and 156:

Figure 8-4.Intel QuickPath Intercon

- Page 157 and 158:

9 System Manageability9.1 Introduct

- Page 159 and 160:

10 Thermal Throttling10.1 OverviewT

- Page 161 and 162:

Figure 10-2. Load Line Distribution

- Page 163 and 164:

headroom because the die is heating

- Page 165 and 166:

11 Power Management11.1 Introductio

- Page 167 and 168:

Table 11-1.Intel Xeon 5500 Platform

- Page 169 and 170:

4. The ICH responds to the SLP_EN w

- Page 171 and 172:

11.5.1 Power Management MessagesWhe

- Page 173 and 174:

12 Intel ® Management EngineThis s

- Page 175 and 176:

13 Reset13.1 IntroductionThis chapt

- Page 177 and 178:

13.1.3 Trigger and Reset Type Assoc

- Page 179 and 180:

Figure 13-1. Physical Layer Power-U

- Page 181 and 182:

13.3 Platform Timing DiagramsFigure

- Page 183 and 184:

Table 13-2.Core Power-Up, Core POWE

- Page 185 and 186:

14 Component Clocking14.1 Component

- Page 187 and 188:

Table 5-1. Clock Pins (Sheet 2 of 2

- Page 189 and 190:

15 Reliability, Availability,Servic

- Page 191 and 192:

15.3 IOH RAS SupportThe IOH core RA

- Page 193 and 194:

15.4.1.1.1 Correctable Errors (Seve

- Page 195 and 196:

The IOH PCI Express root ports can

- Page 197 and 198:

15.4.2.2.5 Error Pins[2:0]The IOH p

- Page 199 and 200:

15.4.3.1 Local Error RegistersEach

- Page 201 and 202:

Global Log Registers (GFFERRST, GNF

- Page 203 and 204:

Figure 15-6. Thermalert and Thermtr

- Page 205 and 206:

Figure 15-7. IOH Error Logging Flow

- Page 207 and 208:

Figure 15-8. Clearing Global and Lo

- Page 209 and 210:

When the data arrives at the receiv

- Page 211 and 212:

15.6.3.4 Unconnected PortsIf a tran

- Page 213 and 214:

Table 15-2.IOH Default Error Severi

- Page 215 and 216:

Table 15-3.IOH Error Summary (Sheet

- Page 217 and 218:

Table 15-3.IOH Error Summary (Sheet

- Page 219 and 220:

Table 15-3.IOH Error Summary (Sheet

- Page 221 and 222:

Table 15-3.IOH Error Summary (Sheet

- Page 223 and 224:

Table 15-3.IOH Error Summary (Sheet

- Page 225 and 226:

Figure 15-11.IOH PCI Express Hot-Pl

- Page 227 and 228:

15.8.1.2 PCI Express Hot-Plug Inter

- Page 229 and 230:

15.9 Virtual Pin Ports (VPP)The IOH

- Page 231 and 232:

The IOH issues Read Commands to upd

- Page 233 and 234:

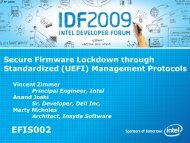

16 Intel ® VirtualizationTechnolog

- Page 235 and 236:

17 Signal ListThis chapter lists al

- Page 237 and 238:

Table 17-5. Intel QuickPath Interco

- Page 239 and 240:

Table 17-7. DDR Signals (Sheet 2 of

- Page 241 and 242:

Table 17-9. MISC Signals (Sheet 3 o

- Page 243 and 244:

Table 17-12. Power and Ground (Shee

- Page 245 and 246:

Table 17-16. Suggested Strap Settin

- Page 247 and 248:

17.6 Intel Xeon 5500 Platforms IOH

- Page 249 and 250:

18 DC Electrical SpecificationsIn t

- Page 251 and 252:

1. No test load is necessarily asso

- Page 253 and 254:

Figure 18-1. Differential Measureme

- Page 255 and 256:

19 Configuration Register SpaceThis

- Page 257 and 258:

Table 19-2. Register Attributes Def

- Page 259 and 260:

19.3.2 Register Definitions - Commo

- Page 261 and 262:

Device: 16, 17Function: 0, 1Device:

- Page 263 and 264:

Device:19Function: 0Device: 16, 17F

- Page 265 and 266:

19.3.2.7 CLS: Cacheline Size Regist

- Page 267 and 268:

Device: 19Function: 0Device: 16, 17

- Page 269 and 270:

Device: 20Function: 0-2Offset:44hBi

- Page 271 and 272:

Device: 20Function: 0-2Offset:48hBi

- Page 273 and 274:

Device: 20Function: 0-2Offset:4ChBi

- Page 275 and 276:

Device: 20Function: 0-2Offset:52hBi

- Page 277 and 278:

Device: 20Function: 0-2Offset:54hBi

- Page 279 and 280:

Device: 20Function: 0-2Offset:58hBi

- Page 281 and 282:

Device: 20Function: 0-2Offset:5AhBi

- Page 283 and 284:

Device: 20Function: 0-2Offset:5ChBi

- Page 285 and 286:

Device: 20Function: 0-2Offset:60hBi

- Page 287 and 288:

Device: 20Function: 0-2Offset:72hBi

- Page 289 and 290:

Device: 19Function: 0Offset:04hBit

- Page 291 and 292:

Register: PCISTSDevice: 19Function:

- Page 293 and 294:

19.4.4 ABAR: I/OxAPIC Alternate BAR

- Page 295 and 296:

Register:PMCSRDevice:19Function:0Of

- Page 297 and 298:

Register:IOAPICTETPCDevice:19Functi

- Page 299 and 300:

Register:PMCAPDevice:19Function:0Of

- Page 301 and 302:

19.4.14 RDINDEX: Alternate Index to

- Page 303 and 304:

Table 19-5. I/OxAPIC Direct Memory

- Page 305 and 306:

19.4.22 APICIDThis register uniquel

- Page 307 and 308:

Register: RTL[0:23]BAR: MBAROffset:

- Page 309 and 310:

Table 19-8. Core Registers (Dev 20,

- Page 311 and 312:

Register: IOHMISCCTRLDevice:20Funct

- Page 313 and 314:

19.5.5 DUALIOAPIC.ABAR.BASE: Dual I

- Page 315 and 316:

19.5.7.2 GENPROTRANGE.BASE1: Generi

- Page 317 and 318:

Register: TOLMDevice:20Function:0Of

- Page 319 and 320:

Register: DEVHIDE1Device:20Function

- Page 321 and 322:

Register: DEVHIDE1Device:20Function

- Page 323 and 324:

Register: DEVHIDE1Device:20Function

- Page 325 and 326:

Register: DEVHIDE2Device:20Function

- Page 327 and 328:

19.5.7.16 LMMIOL.LIMIT: Local MMIOL

- Page 329 and 330:

Register: LMMIOH.LIMITUDevice:20Fun

- Page 331 and 332:

19.5.7.26 GMMIOL.LIMIT: Global MMIO

- Page 333 and 334:

19.5.7.30 GMMIOH.LIMITU: Global MMI

- Page 335 and 336:

This register and DUALIOAPIC.ABAR.L

- Page 337 and 338:

19.5.7.38 DUAL.NL.MMIOH.LIMIT: Dual

- Page 339 and 340:

19.5.7.42 DUAL.NL.BUS.LIMIT: Dual N

- Page 341 and 342:

19.5.7.44 VTBAR: Base Address Regis

- Page 343 and 344:

19.5.7.47 VTSTS: Intel VT-d Status

- Page 345 and 346:

19.5.8 Semaphore and Scratch Pad Re

- Page 347 and 348:

19.5.8.2 SR[4:7]: Scratch Pad Regis

- Page 349 and 350:

19.5.8.9 CWR[12:15]: Conditional Wr

- Page 351 and 352:

19.5.8.15 IR[12:15]: Increment Regi

- Page 353 and 354:

)Table 19-11. IOH Control/Status &

- Page 355 and 356:

Table 19-13. IOH Local Error Map #2

- Page 357 and 358:

Register: QPIPERRSVDevice:20Functio

- Page 359 and 360:

Register: PCIERRSVDevice:20Function

- Page 361 and 362:

Register: SYSMAPDevice:20Function:2

- Page 363 and 364:

19.5.9.10 ERRPINST: Error Pin Statu

- Page 365 and 366:

Register: PRSTRDYDevice:20Function:

- Page 367 and 368:

Register: FREQDevice:20Function:2Of

- Page 369 and 370:

19.6.1 Global Error Registers19.6.1

- Page 371 and 372:

Register: GFERRSTDevice:20Function:

- Page 373 and 374:

Register:GERRCTLDevice:20Function:2

- Page 375 and 376:

Register:GSYSCTLDevice:20Function:2

- Page 377 and 378:

19.6.1.13 GNNERRST: Global Non-Fata

- Page 379 and 380:

Table 19-16. IOH Local Error Map #2

- Page 381 and 382:

Register:QPI[1:0]ERRSTDevice:20Func

- Page 383 and 384:

individual error is reported with t

- Page 385 and 386:

Register:QPI[1:0]NNERRSTDevice:20Fu

- Page 387 and 388:

Register:QPIP[1:0]ERRCTLDevice:20Fu

- Page 389 and 390:

19.7.1.14 QPIP[1:0]FNERRST: Intel Q

- Page 391 and 392:

19.7.1.18 QPIP[1:0]NFERRHD: Intel Q

- Page 393 and 394:

Register:IOHERRCTLDevice:20Function

- Page 395 and 396:

19.7.2.6 IOHNFERRHD[0:3]: Local Non

- Page 397 and 398:

Register:THRERRSTDevice:20Function:

- Page 399 and 400:

19.7.3.5 THRNNERRST: Thermal Non-Fa

- Page 401 and 402:

Register:MIERRCTLDevice:20Function:

- Page 403 and 404:

19.7.4.7 MINNERRST: Miscellaneous N

- Page 405 and 406:

Register:QPIP[1:0]FERRLFLIT0Device:

- Page 407 and 408:

19.8.1 Coarse-Grained Clock Gating

- Page 409 and 410:

Register:CGCTRL6Device:20Function:3

- Page 411 and 412:

Register:TSCTRLDevice:20Function:3O

- Page 413 and 414:

19.8.2.7 TSFSC: On-Die Thermal Sens

- Page 415 and 416:

19.10 Intel QuickPath Interconnect

- Page 417 and 418:

Register:QPI[1:0]LCPDevice:17, 16Fu

- Page 419 and 420:

19.10.1.4 QPI[1:0]LS: Intel QuickPa

- Page 421 and 422:

Register:QPI[1:0]LSDevice:17, 16Fun

- Page 423 and 424:

Register:QPI[1:0]LPOC2Device:17, 16

- Page 425 and 426:

Register:QPI[1:0]LCRDCDevice:17, 16

- Page 427 and 428:

Table 19-20. CSR Intel QPI Routing

- Page 429 and 430:

Register:QPIRTBLDevice:16Function:1

- Page 431 and 432:

Register:QPIPCTRLDevice:16Function:

- Page 433 and 434:

Register:QPIPCTRLDevice:16Function:

- Page 435 and 436:

Register: QPIPRTODevice:16Function:

- Page 437 and 438:

Register:QPIPMADCTRLDevice:16Functi

- Page 439 and 440:

Register:QPIPSAPICDDevice:16Functio

- Page 441 and 442:

Register:QPIPLIOSADDevice:16Functio

- Page 443 and 444:

Note:The start of the quiesce opera

- Page 445 and 446:

Register:QPIPLKMSDevice:16Function:

- Page 447 and 448:

19.10.2.24 QPIPNMIC: Intel® QuickP

- Page 449 and 450:

Register:QPIPINTRCDevice:17Function

- Page 451 and 452:

Register:QPIPINTRSDevice:17Function

- Page 453 and 454:

Register: QPI[1:0]PH_CTRDevice: 13F

- Page 455 and 456:

Table 19-23. QPIPH-Intel QuickPath

- Page 457 and 458:

Register: QPI[1:0]EP_MCTRDevice: 13

- Page 459 and 460:

Not all the capabilities listed abo

- Page 461 and 462:

Table 19-26. IOH Devices 0(ESI Mode

- Page 463 and 464:

Table 19-28. IOH Devices 0(PCIe Mod

- Page 465 and 466:

19.11.2.1 VID: Vendor Identificatio

- Page 467 and 468:

Register: PCICMDDevice:0-10Function

- Page 469 and 470:

19.11.2.6 RID: Revision Identificat

- Page 471 and 472:

19.11.2.12 BIST: Built-In Self Test

- Page 473 and 474:

Register: PBUSDevice:0-10Function:0

- Page 475 and 476:

Register: SECSTSDevice:0-10Function

- Page 477 and 478:

Setting the prefetchable memory lim

- Page 479 and 480:

Register:BCRDevice:0-10Function:0Of

- Page 481 and 482:

19.11.4.7 MSICTL: MSI Control Regis

- Page 483 and 484:

Table 19-30. MSI Vector Handling an

- Page 485 and 486:

Register: DEVCAPDevice:0-10Function

- Page 487 and 488:

Register: DEVSTSDevice:0-10Function

- Page 489 and 490:

Register: LNKCONDevice:0-10Function

- Page 491 and 492:

Register: LNKSTSDevice:0-10Function

- Page 493 and 494:

Register: SLTCONDevice:1-10Function

- Page 495 and 496:

Register: SLTCONDevice:1-10Function

- Page 497 and 498:

Register: ROOTCONDevice:0-10Functio

- Page 499 and 500:

Register: DEVCAP2Device:0-10Functio

- Page 501 and 502:

Register: PMCAPDevice:1-10Function:

- Page 503 and 504:

19.11.5 PCI Express Enhanced Config

- Page 505 and 506:

Register: UNCERRSEVDevice:0-10Funct

- Page 507 and 508:

Register: ERRCMDDevice:0-10Function

- Page 509 and 510:

Register: SSMSKDevice:0-10Function:

- Page 511 and 512:

Register:ACSCAPDevice:0-10Function:

- Page 513 and 514:

Register: PERFCTRLSTSDevice:0-10Fun

- Page 515 and 516:

Register: MISCCTRLSTSDevice: 0Funct

- Page 517 and 518:

Register: MISCCTRLSTSDevice: 1-10Fu

- Page 519 and 520:

Register:PCIE_IOU1_BIF_CTRLDevice:7

- Page 521 and 522:

19.12.2 XPCORERRMSK - XP Correctabl

- Page 523 and 524:

19.12.5.2 UNCEDMASK: Uncorrectable

- Page 525 and 526:

19.12.6 XPGLBERRSTS - XP Global Err

- Page 527 and 528:

Register:PCIE_LER_SS_CTRLSTSDevice:

- Page 529 and 530:

Table 19-32. Intel VT-d Memory Mapp

- Page 531 and 532:

Figure 19-2. Base Address of Intel

- Page 533 and 534:

19.13.1.4 GLBCMD: Global Command Re

- Page 535 and 536:

Register: CTXCMDAddr: MMIOBAR: VTBA

- Page 537 and 538:

19.13.1.9 FLTEVTCTRL: Fault Event C

- Page 539 and 540:

19.13.1.15 PROT_LOW_MEM_LIMIT : Pro

- Page 541 and 542:

19.13.1.21 INV_COMP_STATUS: Invalid

- Page 543 and 544:

Register:FLTREC[7:0Addr: MMIOBAR: V

- Page 545 and 546:

Register: INVADDRREGAddr: MMIOBAR:

- Page 547 and 548:

20 Package and BalloutInformation20

- Page 549 and 550:

Figure 20-3. IOH Ballout Center (To

- Page 551 and 552:

Table 20-1. IOH Signals (by Ball Nu

- Page 553 and 554:

Table 20-3. IOH Signals (by Ball Nu

- Page 555 and 556:

Table 20-5. IOH Signals (by Ball Nu

- Page 557 and 558:

Table 20-7. IOH Signals (by Ball Nu

- Page 559 and 560:

Table 20-9. IOH Signals (by Ball Nu

- Page 561 and 562:

Table 20-11. IOH Signals (by Ball N

- Page 563 and 564:

Table 20-13. IOH Signals (by Ball N

- Page 565 and 566:

Table 20-15. IOH Signals (by Ball N

- Page 567 and 568:

Table 20-17. IOH Signals (by Ball N

- Page 569 and 570:

Table 20-19. IOH Signals (By Signal

- Page 571 and 572:

Table 20-21. IOH Signals (by Signal

- Page 573 and 574:

Table 20-23. IOH Signals (by Signal

- Page 575 and 576:

Table 20-25. IOH Signals (by Signal

- Page 577 and 578:

Table 20-27. IOH Signals (by Signal

- Page 579 and 580:

Table 20-29. IOH Signals (by Signal

- Page 581 and 582:

Table 20-31. IOH Signals (by Signal

- Page 583 and 584:

Table 20-33. IOH Signals (by Signal

- Page 585 and 586:

Table 20-35. IOH Signals (by Signal

- Page 587 and 588:

20.3 Intel® 5500 Chipset IOH Ballo

- Page 589 and 590:

Figure 20-6. IOH 24D Ballout Left S

- Page 591 and 592:

Table 20-37. IOH Signals (by Ball N

- Page 593 and 594:

Table 20-39. IOH Signals (by Ball N

- Page 595 and 596:

Table 20-41. IOH Signals (by Ball N

- Page 597 and 598:

Table 20-43. IOH Signals (by Ball N

- Page 599 and 600:

Table 20-45. IOH Signals (by Ball N

- Page 601 and 602:

Table 20-47. IOH Signals (by Ball N

- Page 603 and 604:

Table 20-49. IOH Signals (by Ball N

- Page 605 and 606:

Table 20-51. IOH Signals (by Ball N

- Page 607 and 608:

Table 20-53. IOH Signals (by Ball N

- Page 609 and 610:

Table 20-55. IOH Signals (by Signal

- Page 611 and 612:

Table 20-57. IOH Signals (by Signal

- Page 613 and 614:

Table 20-59. IOH Signals (by Signal

- Page 615 and 616:

Table 20-61. IOH Signals (by Signal

- Page 617 and 618:

Table 20-63. IOH Signals (by Signal

- Page 619 and 620:

Table 20-65. IOH Signals (by Signal

- Page 621 and 622:

Table 20-67. IOH Signals (by Signal

- Page 623 and 624:

Table 20-69. IOH Signals (by Signal

- Page 625 and 626:

Table 20-71. IOH Signals (by Signal

- Page 627 and 628:

20.5 Package InformationFigure 20-8