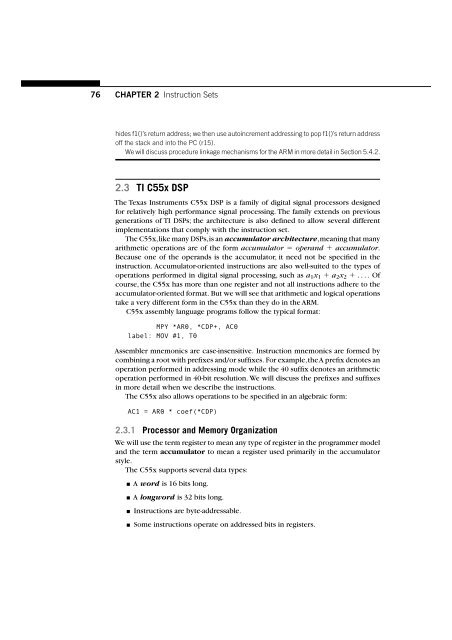

76 CHAPTER 2 <strong>Instruction</strong> <strong>Sets</strong>hides f1()’s return address; we then use autoincrement addressing to pop f1()’s return addressoff the stack and into the PC (r15).We will discuss procedure linkage mechanisms for the ARM in more detail in Section 5.4.2.2.3 TI C55x DSPThe Texas Instruments C55x DSP is a family of digital signal processors designedfor relatively high performance signal processing. The family extends on previousgenerations of TI DSPs; the architecture is also defined to allow several differentimplementations that comply with the instruction set.The C55x,like many DSPs,is an accumulator architecture,meaning that manyarithmetic operations are of the form accumulator operand accumulator.Because one of the operands is the accumulator, it need not be specified in theinstruction. Accumulator-oriented instructions are also well-suited to the types ofoperations performed in digital signal processing, such as a 1 x 1 a 2 x 2 ....Ofcourse, the C55x has more than one register and not all instructions adhere to theaccumulator-oriented format. But we will see that arithmetic and logical operationstake a very different form in the C55x than they do in the ARM.C55x assembly language programs follow the typical format:MPY *AR0, *CDP+, AC0label: MOV #1, T0Assembler mnemonics are case-insensitive. <strong>Instruction</strong> mnemonics are formed bycombining a root with prefixes and/or suffixes. For example,theA prefix denotes anoperation performed in addressing mode while the 40 suffix denotes an arithmeticoperation performed in 40-bit resolution. We will discuss the prefixes and suffixesin more detail when we describe the instructions.The C55x also allows operations to be specified in an algebraic form:AC1 = AR0 * coef(*CDP)2.3.1 Processor and Memory OrganizationWe will use the term register to mean any type of register in the programmer modeland the term accumulator to mean a register used primarily in the accumulatorstyle.The C55x supports several data types:■ A word is 16 bits long.■ A longword is 32 bits long.■■<strong>Instruction</strong>s are byte-addressable.Some instructions operate on addressed bits in registers.

2.3 TI C55x DSP 77The C55x has a number of registers. Few to none of these registers are generalpurposeregisters like those of the ARM. Registers are generally used for specializedpurposes. Because the C55x registers are less regular, we will discuss them by howthey may be used rather than simply listing them.Most registers are memory-mapped—that is,the register has an address in thememory space. A memory-mapped register can be referred to in assembly languagein two different ways: either by referring to its mnemonic name or through itsaddress.The program counter is PC.The program counter extension register XPC extendsthe range of the program counter. The return address register RETA is used forsubroutines.The C55x has four 40-bit accumulators AC0,AC1,AC2, and AC3. The low-orderbits 0–15 are referred to as AC0L,AC1L,AC2L, and AC3L; the high-order bits 16–31are referred to as AC0H, AC1H, AC2H, and AC3H; and the guard bits 32–39 arereferred to as AC0G, AC1G, AC2G, and AC3G. (Guard bits are used in numericalalgorithms like signal processing to provide a larger dynamic range for intermediatecalculations.)The architecture provides six status registers. Three of the status registers,ST0 and ST1 and the processor mode status register PMST, are inherited fromthe C54x architecture. The C55x adds four registers ST0_55, ST1_55, ST2_55,and ST3_55. These registers provide arithmetic and bit manipulation flags, a datapage pointer and auxiliary register pointer, and processor mode bits, among otherfeatures.The stack pointer SP keeps track of the system stack. A separate system stackis maintained through the SSP register. The SPH register is an extended data pagepointer for both SP and SSP.Eight auxiliary registers AR0AR7 are used by several types of instructions,notably for circular buffer operations. The coefficient data pointer CDP is usedto read coefficients for polynomial evaluation instructions; CDPH is the main datapage pointer for the CDP.The circular buffer size register BK47 is used for circular buffer operations for theauxiliary registers AR4–7. Four registers define the start of circular buffers: BSA01for auxiliary registers AR0 and AR1; BSA23 for AR2 and AR3; BSA45 for AR4 and AR5;BSA67 for AR6 and AR7. The circular buffer size register BK03 is used to addresscircular buffers that are commonly used in signal processing. BKC is the circularbuffer size register for CDP. BSAC is the circular buffer coefficient start addressregister.Repeats of single instructions are controlled by the single repeat register CSR.This counter is the primary interface to the program. It is loaded with the requirednumber of iterations. When the repeat starts, the value in CSR is copied into therepeat counter RPTC, which maintains the counts for the current repeat and isdecremented during each iteration.Several registers are used for block repeats—instructions that are executed severaltimes in a row. The block repeat counter BRC0 counts block repeat iterations.