Prof. Dr. Thomas Baier DG8SAQ - SDR-Kits

Prof. Dr. Thomas Baier DG8SAQ - SDR-Kits

Prof. Dr. Thomas Baier DG8SAQ - SDR-Kits

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

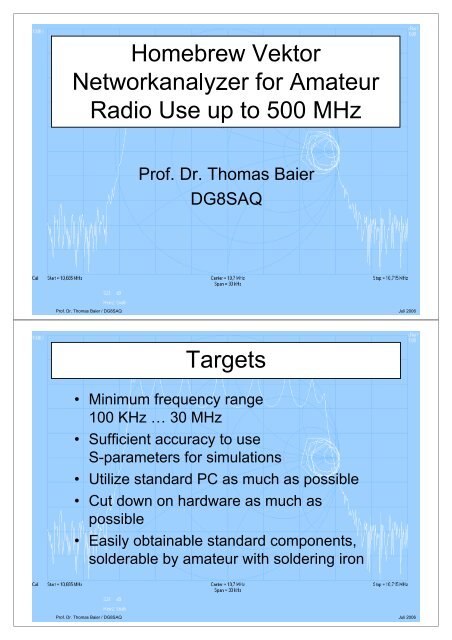

<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong><strong>DG8SAQ</strong><strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006• Minimum frequency range100 KHz … 30 MHz• Sufficient accuracy to useS-parameters for simulations• Utilize standard PC as much as possible• Cut down on hardware as much aspossible• Easily obtainable standard components,solderable by amateur with soldering iron<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006

<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006

≈ 30 kHz<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006‣ Usable frequency range: 200 Hz … about 500 MHz‣ Exceptions:Zero signal amplitude in vicinitiy of integer multiplesof DDS clock frequency (180MHz, 360 MHz, 540 MHz …)→ measurements not possible≈ 30 kHz<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006

RF50Bridge Voltage5050501 : 1BALUN50Z S = 50DUTProblem:Solution:make wideband BALUNuse balanced Gilbert Cell Mixer<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006LOIF+ IF -RF+RF-<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006

LO DDSReference Signal= Bridge Current+-8,2NE6121510RF DDSZ S = ∞LO DDSBridgeVoltage+-NE61210 FTantal27Z S = 50,2DUTProblem: Frequenzgang des DC-Blocks im Hz - Bereich<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006to Parallel Interface to Line In +12V/250mA DC100mmTX<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006RX

<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006

… e.g. with APLAC:Circuit Diagram [...] (E)Sweep Init (E)Sweep"Initial analysis"LOOP 400 FREQ LIN 10.685Meg 10.714925MegW 0 Y "Gain" "dB" -30 0W 1 SMITHLOAD "F64A.s1p"Show+ W 0 Y MagdB(S(2,1))+ W 0 Y MagdB(S(1,1))+ W 0 Y MagdB(S(2,2))+ W 1 DB S(1,1)+ DB S(2,2)EndSweepport_1270ohmport_2270ohmLOAD "F64B.s1p"<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 20060.00Initial analysisAPLAC 8.00 Student version FOR NON-COMMERCIAL USE ONLYGain-7.50dB-15.00-22.50-30.0010.685M 10.692M 10.700M 10.707M 10.715Mf/HzMagdB(S(2,1))MagdB(S(1,1))MagdB(S(2,2))<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006

HP8753CsoftwarematchedVNWAsoftwarematchedVNWAZ S= Z L= 50 Ω<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006simulated matchingresistive matchingZ S= Z L= 610 Ωe.g. 11 kHz LC FilterZ S= Z L= 50 Ω<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006

e.g. 400 MHz SAW FilterVNWAHP8753CVerbesserung durch 10 dB Dämpfungsglied vor RX-Eingang<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006Achieved:• 200 Hz – 500 MHz covered with exceptions,especially VLF-2m, 70cm covered!• Accuracy sufficient for network synthesis.• Minimum hardware, no tuning points.• Universal software• Principally achievable accuracy with PC sounddevice: 0,01dB and 0,1°,currently limited by Mixer nonlinearitiesPossible Improvements:• Higher level mixers• DDS devices with higher clock rates (up to 1 GHz)<strong>Prof</strong>. <strong>Dr</strong>. <strong>Thomas</strong> <strong>Baier</strong> / <strong>DG8SAQ</strong> Juli 2006