- Page 1 and 2: Logi. Deconpolltlon eitt T.chmto$/

- Page 3 and 4: }Iehren UtrireEity off,ngireering &

- Page 5 and 6: TABLE OF CONTENTS Ch.Dl.r I INTRODU

- Page 7 and 8: 5.7.1 CLUSTER.FXIA AllI t!ct!r! 5.7

- Page 9 and 10: LISTOFTABLES Table 2. | : Coricctio

- Page 11 and 12: Fie!re.2.101 liigue,2.ll i Iigure 3

- Page 13 and 14: AASTRACT Sin e lst two daades. Fi

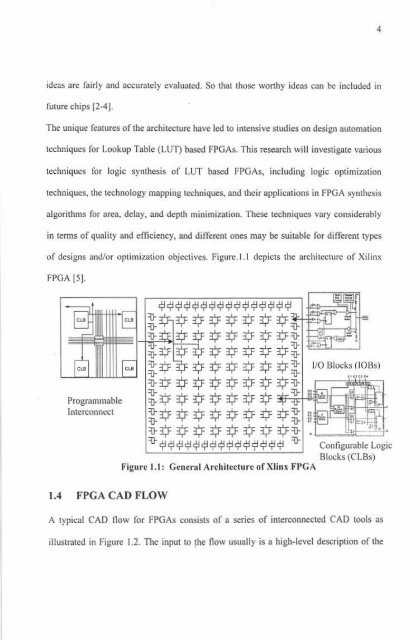

- Page 15: nN. FPCA CAD !6ls !E nmh chcrF lo.c

- Page 19 and 20: togcther by deleninins rhe cohfigur

- Page 21 and 22: cniciency. Al$. in llal n wN st$uhl

- Page 23 and 24: SdtioN 4.5 dd 4.6 €laboEr. key d.

- Page 25 and 26: 2.2 FPGA ARCHITECTURE TERMINOLOGY A

- Page 27 and 28: Fi8ua 2.4 shows ! small ponion otd

- Page 29 and 30: '''1 . Th. black squares nark block

- Page 31 and 32: curcs stored ror cach ncr (rhis rcd

- Page 33 and 34: lwo-lefrinal nels rhar ae part of $

- Page 35 and 36: wi$ir1r*icc the cosl ofthc optimalS

- Page 37 and 38: lo dclly reelulion. ncls thnt ae p.

- Page 39 and 40: 9/. les lEcks Fr chdncl, oh .v.nge.

- Page 41 and 42: it.rorion of tne rourer. all of the

- Page 43 and 44: enhdcenents. The tiur enhdcem.fl is

- Page 45 and 46: silk. rDd.iusl lD ncw ponion ofrhc

- Page 47 and 48: all rhe nodes in the cunent exp.nsi

- Page 49 and 50: Using a model ollbe Xilinx 4000 XL

- Page 51 and 52: Iigrr2.9:ILr. .dtl4of rXC,{X'|,F./X

- Page 53 and 54: qudd-length egm.nls iotrre insroups

- Page 55 and 56: CIIAPTER.} FIELD PROGRAMMABLE GATE

- Page 57 and 58: { nurcd lo rnt ol dE lbur 4,|-ljT!f

- Page 59 and 60: . splir inro qurneN. wc cho* ro pld

- Page 61 and 62: Pal(-d,r,, isthetotal of rhcco$of l

- Page 63 and 64: sho*n in grd,. woold two morc sgn.n

- Page 65 and 66: o(ler h cxlEn.ly di@ld rnd *ill !@p

- Page 67 and 68:

In the pEence ofsigniticanr ouring

- Page 69 and 70:

trEt otrtr fto D oo tr o tr 0troo o

- Page 71 and 72:

tim.shnstoincl!¬ice.blt*h.nthcMB

- Page 73 and 74:

ollN.bhsizc$ali|uri(loK, lhccruulin

- Page 75 and 76:

2. lo 400, conlpored ro tror binoin

- Page 77 and 78:

3tu8 quadEri€lly a rhe nunb.. or

- Page 79 and 80:

To dd.mine rhe b.sr vdrc ls $. hctr

- Page 81 and 82:

cstxmiotr onctutnnrs nquirud hy sri

- Page 83 and 84:

tlE qo*llengrh or long-logrh $8hc.r

- Page 85 and 86:

leb. This Eduas rh. si4 ot inc da@d

- Page 87 and 88:

vPR hd a buih in dcl.y estimdor lha

- Page 89 and 90:

h FiguE4,3 *e siow expcinenEt rcsul

- Page 91 and 92:

loSic irro fic clue6. Sine w G Bins

- Page 93 and 94:

This lcin onc outpur lM 4h chuing l

- Page 95 and 96:

avcEes oi $. r6ulB lor rh* cncuiG.

- Page 97 and 98:

FiguE4.8 shows th.t ci(uil spcd inc

- Page 99 and 100:

!< -':! 6i ,E 3 5 l I 0 Ionr

- Page 101 and 102:

, l! s ol tr q oE' FisuE 4.12 Dft'l

- Page 103 and 104:

CHAPTER 5 CLUSTER.BASED FPGA ROUTIN

- Page 105 and 106:

connFtion bus A. Connection B rh.n

- Page 107 and 108:

clu$er conlainine rhe laeer chBler,

- Page 109 and 110:

A supetuluster conbiiiis M cluseN h

- Page 111 and 112:

slgorithm 6 dcsrib€d in 04lj .cv.

- Page 113 and 114:

An qanDl.ofa pin-bus is illusrEr.d

- Page 115 and 116:

and de d.lrt con. h is al$ a fu@tio

- Page 117 and 118:

m Dm .lh.cilk0lplth d.layoflhcciEui

- Page 119 and 120:

orioh dnd I buses on rhe left side

- Page 121 and 122:

where lhc aveEgc numbcr of lin .gmi

- Page 123 and 124:

duc to thc fel lhat th. area eticie

- Page 125 and 126:

6.I BENCHMARK CIRCUITS RESULTS AND

- Page 127 and 128:

5 I 3 2 t 0 --.- 2 --.- 3 --*- 5 t-

- Page 129 and 130:

The rcsulrs illusbre rhar rhe tocat

- Page 131 and 132:

The sond k y meric fo. FPCtu is rhe

- Page 133 and 134:

P1s incRed 4 .rd 5 tlm @nnedtu e qf

- Page 135 and 136:

For exmplc, li.eosilg rhc cluslo da

- Page 137 and 138:

miny dcadenic srudi.s ed starc-oh&d

- Page 139 and 140:

t&ls pn chann.l. By adding lhr$ 40

- Page 141 and 142:

th. FPGA 4. is nainly dominat.d by

- Page 143 and 144:

clu$er size k incGasd lom I ro I An

- Page 145 and 146:

l|!{& c Equftd ft. tutl uliti4rir!

- Page 147 and 148:

Ficld.PBs.ammrblc Losic md Appticar

- Page 149 and 150:

I27l Lee. Y.S.. wu, A. 'A FPOAScors

- Page 151 and 152:

Arp.rilL E AeD..db E APPEI\DICES Ts

- Page 153 and 154:

Trbre A,2: Torrt atu (rt01h Min. wt

- Page 155 and 156:

T.ble A"4: Tor.l Ar! (! rol i! MI.,

- Page 157 and 158:

T,blc ,{.6: Tolll Arc{ (xloi) tn Mi

- Page 159 and 160:

Anncndix B Inlra clusler logic rrea

- Page 161 and 162:

frbl. Bl: I n-Clurler aEr (xr05 ir

- Page 163 and 164:

T,bk 4.5: Inrn-Cl$t.r,{hr(xlo!) I!

- Page 165 and 166:

T!bl.8.7: li.n-crlrrera..r (rt4 in

- Page 167 and 168:

Tablc c,2: lnrcr-chrt$ arc! (rro in

- Page 169 and 170:

Trbl. c.a: lr|FclBrcr AM (rl01i. Mi

- Page 171 and 172:

Trbrc c.6: I irer-ctBrer ^Er (rro1

- Page 173 and 174:

Apoendix D Total Critic.l Path Deta

- Page 175 and 176:

T.bl. D,3: Tot.l Del.y in n.m{(obd!

- Page 177 and 178:

T.blc D.5: Totrl Dehy i! nrescondr

- Page 179 and 180:

T,ble D,?: Totrl Oelr' ln n.no+{ond

- Page 181 and 182:

T.bl. E.2. htn-clus..r D.l.y i! !.!

- Page 183 and 184:

Tlblc 8.4: lnrm-Closter D.l.y in ro

- Page 185 and 186:

T{bl.E.6: rntr.-Chrte. D.lry In orn

- Page 187 and 188:

Appendix F Inlcr-Cluster Del, for t

- Page 189 and 190:

Ttbl. F.3: Inter-Clulier D.hy in mn

- Page 191 and 192:

Trble F,5: lnr.r-ClBt.rDehy iI n.ro

- Page 193 and 194:

Tible F.?: Int .-Clurl.. Dehy in m.

- Page 195 and 196:

Analysis ard Comparison ofSynthesis

- Page 197 and 198:

o9!hi!.d *i$ espct to arim$d iBpl.m

- Page 199 and 200:

2-6 EdgFMsP Edtc.M.t *r! d.v!lo!.d

- Page 201 and 202:

{ f.Tn bh.k !q@3 ruk blsk ! i.dqsdo

- Page 203 and 204:

fl 4J CGE v€sB SEGA Ih. sE6A 6uri

- Page 205 and 206:

llirl ''l4fu^s|dded.i'.'Mi4d& Mu4ri