Rezumat teza Alin Tisan - Facultatea de Electronica ...

Rezumat teza Alin Tisan - Facultatea de Electronica ...

Rezumat teza Alin Tisan - Facultatea de Electronica ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Rezumat</strong> pag. 7<br />

‐ Blocul generator eta_beta: blocul ce <strong>de</strong>termină funcţiei <strong>de</strong> scalare a pon<strong>de</strong>rilor ,( ) () h t şi calculează<br />

mărimea vecinătăţii β () t .<br />

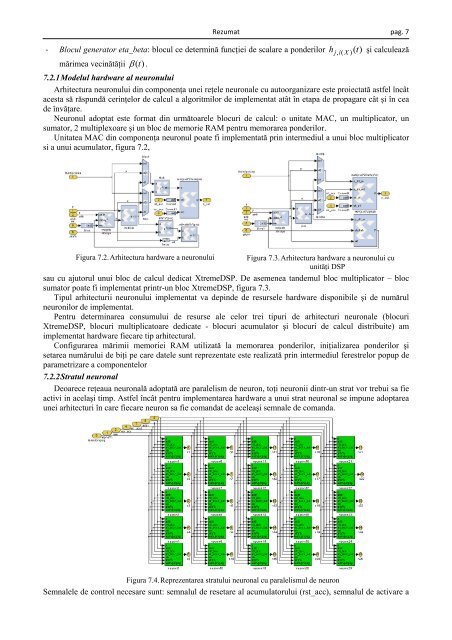

7.2.1 Mo<strong>de</strong>lul hardware al neuronului<br />

Arhitectura neuronului din componenţa unei reţele neuronale cu autoorganizare este proiectată astfel încât<br />

acesta să răspundă cerinţelor <strong>de</strong> calcul a algoritmilor <strong>de</strong> implementat atât în etapa <strong>de</strong> propagare cât şi în cea<br />

<strong>de</strong> învăţare.<br />

Neuronul adoptat este format din următoarele blocuri <strong>de</strong> calcul: o unitate MAC, un multiplicator, un<br />

sumator, 2 multiplexoare şi un bloc <strong>de</strong> memorie RAM pentru memorarea pon<strong>de</strong>rilor.<br />

Unitatea MAC din componenţa neuronul poate fi implementată prin intermediul a unui bloc multiplicator<br />

si a unui acumulator, figura 7.2,<br />

Figura 7.2. Arhitectura hardware a neuronului Figura 7.3. Arhitectura hardware a neuronului cu<br />

unităţi DSP<br />

sau cu ajutorul unui bloc <strong>de</strong> calcul <strong>de</strong>dicat XtremeDSP. De asemenea tan<strong>de</strong>mul bloc multiplicator – bloc<br />

sumator poate fi implementat printr-un bloc XtremeDSP, figura 7.3.<br />

Tipul arhitecturii neuronului implementat va <strong>de</strong>pin<strong>de</strong> <strong>de</strong> resursele hardware disponibile şi <strong>de</strong> numărul<br />

neuronilor <strong>de</strong> implementat.<br />

Pentru <strong>de</strong>terminarea consumului <strong>de</strong> resurse ale celor trei tipuri <strong>de</strong> arhitecturi neuronale (blocuri<br />

XtremeDSP, blocuri multiplicatoare <strong>de</strong>dicate - blocuri acumulator şi blocuri <strong>de</strong> calcul distribuite) am<br />

implementat hardware fiecare tip arhitectural.<br />

Configurarea mărimii memoriei RAM utilizată la memorarea pon<strong>de</strong>rilor, iniţializarea pon<strong>de</strong>rilor şi<br />

setarea numărului <strong>de</strong> biţi pe care datele sunt reprezentate este realizată prin intermediul ferestrelor popup <strong>de</strong><br />

parametrizare a componentelor<br />

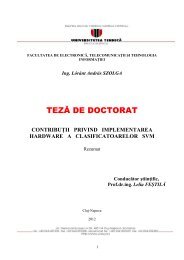

7.2.2 Stratul neuronal<br />

Deoarece reţeaua neuronală adoptată are paralelism <strong>de</strong> neuron, toţi neuronii dintr-un strat vor trebui sa fie<br />

activi in acelaşi timp. Astfel încât pentru implementarea hardware a unui strat neuronal se impune adoptarea<br />

unei arhitecturi în care fiecare neuron sa fie comandat <strong>de</strong> aceleaşi semnale <strong>de</strong> comanda.<br />

Figura 7.4. Reprezentarea stratului neuronal cu paralelismul <strong>de</strong> neuron<br />

Semnalele <strong>de</strong> control necesare sunt: semnalul <strong>de</strong> resetare al acumulatorului (rst_acc), semnalul <strong>de</strong> activare a<br />

ji X