Rezumat teza Alin Tisan - Facultatea de Electronica ...

Rezumat teza Alin Tisan - Facultatea de Electronica ...

Rezumat teza Alin Tisan - Facultatea de Electronica ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

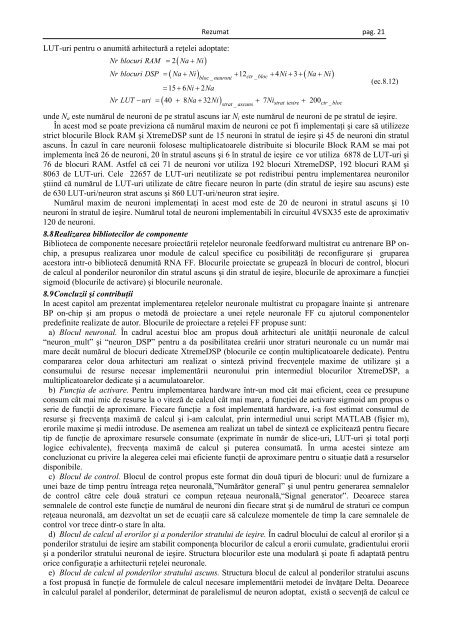

<strong>Rezumat</strong> pag. 21<br />

LUT-uri pentru o anumită arhitectură a reţelei adoptate:<br />

Nr blocuri RAM = 2(<br />

Na + Ni)<br />

Nr blocuri DSP = Na + Ni + 12 + 4Ni + 3 + Na + Ni<br />

( ) ( )<br />

bloc _ neuroni<br />

( )<br />

strat _ ascuns<br />

ctr _ bloc<br />

Nr LUT − uri =<br />

= 15 + 6Ni + 2Na<br />

40 + 8Na + 32 Ni + 7 Ni + 200<br />

strat iesire ctr _bloc<br />

(ec.8.12)<br />

un<strong>de</strong> Na este numărul <strong>de</strong> neuroni <strong>de</strong> pe stratul ascuns iar Ni este numărul <strong>de</strong> neuroni <strong>de</strong> pe stratul <strong>de</strong> ieşire.<br />

În acest mod se poate previziona că numărul maxim <strong>de</strong> neuroni ce pot fi implementaţi şi care să utilizeze<br />

strict blocurile Block RAM şi XtremeDSP sunt <strong>de</strong> 15 neuroni în stratul <strong>de</strong> ieşire şi 45 <strong>de</strong> neuroni din stratul<br />

ascuns. În cazul în care neuronii folosesc multiplicatoarele distribuite si blocurile Block RAM se mai pot<br />

implementa încă 26 <strong>de</strong> neuroni, 20 în stratul ascuns şi 6 în stratul <strong>de</strong> ieşire ce vor utiliza 6878 <strong>de</strong> LUT-uri şi<br />

76 <strong>de</strong> blocuri RAM. Astfel că cei 71 <strong>de</strong> neuroni vor utiliza 192 blocuri XtremeDSP, 192 blocuri RAM şi<br />

8063 <strong>de</strong> LUT-uri. Cele 22657 <strong>de</strong> LUT-uri neutilizate se pot redistribui pentru implementarea neuronilor<br />

ştiind că numărul <strong>de</strong> LUT-uri utilizate <strong>de</strong> către fiecare neuron în parte (din stratul <strong>de</strong> ieşire sau ascuns) este<br />

<strong>de</strong> 630 LUT-uri/neuron strat ascuns şi 860 LUT-uri/neuron strat ieşire.<br />

Numărul maxim <strong>de</strong> neuroni implementaţi în acest mod este <strong>de</strong> 20 <strong>de</strong> neuroni in stratul ascuns şi 10<br />

neuroni în stratul <strong>de</strong> ieşire. Numărul total <strong>de</strong> neuroni implementabili în circuitul 4VSX35 este <strong>de</strong> aproximativ<br />

120 <strong>de</strong> neuroni.<br />

8.8 Realizarea bibliotecilor <strong>de</strong> componente<br />

Biblioteca <strong>de</strong> componente necesare proiectării reţelelor neuronale feedforward multistrat cu antrenare BP onchip,<br />

a presupus realizarea unor module <strong>de</strong> calcul specifice cu posibilităţi <strong>de</strong> reconfigurare şi gruparea<br />

acestora intr-o bibliotecă <strong>de</strong>numită RNA FF. Blocurile proiectate se grupează în blocuri <strong>de</strong> control, blocuri<br />

<strong>de</strong> calcul al pon<strong>de</strong>rilor neuronilor din stratul ascuns şi din stratul <strong>de</strong> ieşire, blocurile <strong>de</strong> aproximare a funcţiei<br />

sigmoid (blocurile <strong>de</strong> activare) şi blocurile neuronale.<br />

8.9 Concluzii şi contribuţii<br />

In acest capitol am prezentat implementarea reţelelor neuronale multistrat cu propagare înainte şi antrenare<br />

BP on-chip şi am propus o metodă <strong>de</strong> proiectare a unei reţele neuronale FF cu ajutorul componentelor<br />

pre<strong>de</strong>finite realizate <strong>de</strong> autor. Blocurile <strong>de</strong> proiectare a reţelei FF propuse sunt:<br />

a) Blocul neuronal. În cadrul acestui bloc am propus două arhitecturi ale unităţii neuronale <strong>de</strong> calcul<br />

“neuron_mult” şi “neuron_DSP” pentru a da posibilitatea creării unor straturi neuronale cu un număr mai<br />

mare <strong>de</strong>cât numărul <strong>de</strong> blocuri <strong>de</strong>dicate XtremeDSP (blocurile ce conţin multiplicatoarele <strong>de</strong>dicate). Pentru<br />

compararea celor doua arhitecturi am realizat o sinteză privind frecvenţele maxime <strong>de</strong> utilizare şi a<br />

consumului <strong>de</strong> resurse necesar implementării neuronului prin intermediul blocurilor XtremeDSP, a<br />

multiplicatoarelor <strong>de</strong>dicate şi a acumulatoarelor.<br />

b) Funcţia <strong>de</strong> activare. Pentru implementarea hardware într-un mod cât mai eficient, ceea ce presupune<br />

consum cât mai mic <strong>de</strong> resurse la o viteză <strong>de</strong> calcul cât mai mare, a funcţiei <strong>de</strong> activare sigmoid am propus o<br />

serie <strong>de</strong> funcţii <strong>de</strong> aproximare. Fiecare funcţie a fost implementată hardware, i-a fost estimat consumul <strong>de</strong><br />

resurse şi frecvenţa maximă <strong>de</strong> calcul şi i-am calculat, prin intermediul unui script MATLAB (fişier m),<br />

erorile maxime şi medii introduse. De asemenea am realizat un tabel <strong>de</strong> sinteză ce explicitează pentru fiecare<br />

tip <strong>de</strong> funcţie <strong>de</strong> aproximare resursele consumate (exprimate în număr <strong>de</strong> slice-uri, LUT-uri şi total porţi<br />

logice echivalente), frecvenţa maximă <strong>de</strong> calcul şi puterea consumată. În urma acestei sinteze am<br />

concluzionat cu privire la alegerea celei mai eficiente funcţii <strong>de</strong> aproximare pentru o situaţie dată a resurselor<br />

disponibile.<br />

c) Blocul <strong>de</strong> control. Blocul <strong>de</strong> control propus este format din două tipuri <strong>de</strong> blocuri: unul <strong>de</strong> furnizare a<br />

unei baze <strong>de</strong> timp pentru întreaga reţea neuronală,”Numărător general” şi unul pentru generarea semnalelor<br />

<strong>de</strong> control către cele două straturi ce compun reţeaua neuronală,“Signal generator”. Deoarece starea<br />

semnalele <strong>de</strong> control este funcţie <strong>de</strong> numărul <strong>de</strong> neuroni din fiecare strat şi <strong>de</strong> numărul <strong>de</strong> straturi ce compun<br />

reţeaua neuronală, am <strong>de</strong>zvoltat un set <strong>de</strong> ecuaţii care să calculeze momentele <strong>de</strong> timp la care semnalele <strong>de</strong><br />

control vor trece dintr-o stare în alta.<br />

d) Blocul <strong>de</strong> calcul al erorilor şi a pon<strong>de</strong>rilor stratului <strong>de</strong> ieşire. În cadrul blocului <strong>de</strong> calcul al erorilor şi a<br />

pon<strong>de</strong>rilor stratului <strong>de</strong> ieşire am stabilit componenţa blocurilor <strong>de</strong> calcul a erorii cumulate, gradientului erorii<br />

şi a pon<strong>de</strong>rilor stratului neuronal <strong>de</strong> ieşire. Structura blocurilor este una modulară şi poate fi adaptată pentru<br />

orice configuraţie a arhitecturii reţelei neuronale.<br />

e) Blocul <strong>de</strong> calcul al pon<strong>de</strong>rilor stratului ascuns. Structura blocul <strong>de</strong> calcul al pon<strong>de</strong>rilor stratului ascuns<br />

a fost propusă în funcţie <strong>de</strong> formulele <strong>de</strong> calcul necesare implementării meto<strong>de</strong>i <strong>de</strong> învăţare Delta. Deoarece<br />

în calculul paralel al pon<strong>de</strong>rilor, <strong>de</strong>terminat <strong>de</strong> paralelismul <strong>de</strong> neuron adoptat, există o secvenţă <strong>de</strong> calcul ce